# Investigating Tools and Techniques for Improving Software Performance on Multiprocessor Computer Systems

A thesis submitted in fulfilment of the requirements for the degree of

MASTER OF SCIENCE

of

RHODES UNIVERSITY

by

WAIDE BARRINGTON TRISTRAM

Grahamstown, South Africa March 2011

#### **Abstract**

The availability of modern commodity multicore processors and multiprocessor computer systems has resulted in the widespread adoption of parallel computers in a variety of environments, ranging from the home to workstation and server environments in particular. Unfortunately, parallel programming is harder and requires more expertise than the traditional sequential programming model. The variety of tools and parallel programming models available to the programmer further complicates the issue. The primary goal of this research was to identify and describe a selection of parallel programming tools and techniques to aid novice parallel programmers in the process of developing efficient parallel C/C++ programs for the Linux platform. This was achieved by highlighting and describing the key concepts and hardware factors that affect parallel programming, providing a brief survey of commonly available software development tools and parallel programming models and libraries, and presenting structured approaches to software performance tuning and parallel programming. Finally, the performance of several parallel programming models and libraries was investigated, along with the programming effort required to implement solutions using the respective models.

A quantitative research methodology was applied to the investigation of the performance and programming effort associated with the selected parallel programming models and libraries, which included automatic parallelisation by the compiler, Boost Threads, Cilk Plus, OpenMP, POSIX threads (Pthreads), and Threading Building Blocks (TBB). Additionally, the performance of the GNU C/C++ and Intel C/C++ compilers was examined. The results revealed that the choice of parallel programming model or library is dependent on the type of problem being solved and that there is no overall best choice for all classes of problem. However, the results also indicate that parallel programming models with higher levels of abstraction require less programming effort and provide similar performance compared to explicit threading models.

The principle conclusion was that the problem analysis and parallel design are an important factor in the selection of the parallel programming model and tools, but that models with higher levels of abstractions, such as OpenMP and Threading Building Blocks, are favoured.

#### **ACM Computing Classification System Classification**

Thesis classification under the ACM Computing Classification System (1998 version, valid through 2011) [2]:

**D.1.3** [Concurrent Programming]: Parallel programming

**D.2.5** [Testing and Debugging]: Debugging aids

**D.2.8** [Metrics]: Performance measures, Product metrics

**D.3.3** [Language Constructs and Features]: Concurrent programming structures

General-Terms: Design, Experimentation, Measurement, Performance

#### Acknowledgements

I acknowledge the financial and technical support of Telkom SA, Business Connexion, Comverse SA, Verso Technologies, Stortech, Tellabs, Amatole Telecom Services, Mars Technologies, Bright Ideas Projects 39, and THRIP through the Telkom Centre of Excellence in the Department of Computer Science at Rhodes University. In particular, I extend thanks to Telkom for the generous Centre of Excellence bursary allocated to me during the course of my research.

I am also deeply grateful to my supervisor, Dr Karen Bradshaw, for her exceptional support, advice, and patience. I could not have asked for a better supervisor to guide me through my research.

A special thanks goes to my partner, Lisa, for her love, support and patience, particularly during the final stages of my thesis write-up. Had it not been for her exceptional organisational skills and forward planning, I would have had a significantly harder time finalising this thesis.

Many thanks to my family and friends for their constant support and encouragement.

# **Contents**

| 1 | Intr | oductio | n                                               | 1  |

|---|------|---------|-------------------------------------------------|----|

|   | 1.1  | Proble  | m Statement and Research Goals                  | 2  |

|   | 1.2  | Thesis  | Organisation                                    | 3  |

| 2 | Bacl | kground | d Work                                          | 5  |

|   | 2.1  | Introdu | uction                                          | 5  |

|   | 2.2  | Paralle | el Programming Terms and Concepts               | 6  |

|   |      | 2.2.1   | Serial Computing                                | 6  |

|   |      | 2.2.2   | Parallel Computing                              | 6  |

|   |      | 2.2.3   | Tasks                                           | 7  |

|   |      | 2.2.4   | Processes and Threads                           | 7  |

|   |      | 2.2.5   | Locks                                           | 8  |

|   |      | 2.2.6   | Critical Sections, Barriers and Synchronisation | 8  |

|   |      | 2.2.7   | Race Conditions                                 | 10 |

|   |      | 2.2.8   | Deadlock                                        | 11 |

|   |      | 2.2.9   | Starvation and Livelock                         | 12 |

|   | 2.3  | Paralle | el Performance                                  | 12 |

|   |      | 2.3.1   | Speedup                                         | 13 |

|   |      | 2.3.2   | Amdahl's Law                                    | 14 |

|   |      | 2.3.3   | Gustafson's Law                                 | 15 |

*CONTENTS* ii

|   |      | 2.3.4     | Sequential Algorithms versus Parallel Algorithms | 18 |

|---|------|-----------|--------------------------------------------------|----|

|   | 2.4  | Comp      | uter Organisation                                | 18 |

|   |      | 2.4.1     | Processor Organisation                           | 19 |

|   |      | 2.4.2     | Computer Memory                                  | 29 |

|   |      | 2.4.3     | Memory Organisation                              | 37 |

|   | 2.5  | Mutex     | es, Semaphores and Barriers                      | 40 |

|   |      | 2.5.1     | Properties of Concurrent Operations and Locks    | 40 |

|   |      | 2.5.2     | Atomic Operations                                | 42 |

|   |      | 2.5.3     | Locking Strategies                               | 45 |

|   |      | 2.5.4     | Types of Locks                                   | 46 |

|   | 2.6  | Softwa    | are Metrics                                      | 49 |

|   |      | 2.6.1     | Code Size and Complexity                         | 50 |

|   |      | 2.6.2     | Concluding Remarks                               | 55 |

|   | 2.7  | Summ      | ary                                              | 55 |

| 3 | Para | allel Pro | ogramming Tools                                  | 57 |

|   | 3.1  | Introdu   | action                                           | 57 |

|   | 3.2  | C and     | C++                                              | 57 |

|   |      | 3.2.1     | C++0x                                            | 59 |

|   | 3.3  | Concu     | rrent Programming Environments                   | 59 |

|   |      | 3.3.1     | POSIX Threads                                    | 60 |

|   |      | 3.3.2     | Boost Threads Library                            | 61 |

|   |      | 3.3.3     | Threading Building Blocks                        | 63 |

|   |      | 3.3.4     | OpenMP                                           | 65 |

|   |      | 3.3.5     | Cilk, Cilk++, and Cilk Plus                      | 69 |

|   |      | 3.3.6     | Parallel Performance Libraries                   | 71 |

*CONTENTS* iii

|   | 3.4  | Compi     | ilers                                          | 73  |

|---|------|-----------|------------------------------------------------|-----|

|   |      | 3.4.1     | GNU Compiler Collection                        | 74  |

|   |      | 3.4.2     | Intel C and C++ Compilers                      | 75  |

|   |      | 3.4.3     | Low Level Virtual Machine (LLVM)               | 76  |

|   | 3.5  | Integra   | ated Development Environments                  | 77  |

|   |      | 3.5.1     | Eclipse                                        | 77  |

|   |      | 3.5.2     | NetBeans IDE                                   | 78  |

|   | 3.6  | Debug     | ging and Profiling Tools                       | 80  |

|   |      | 3.6.1     | GNU Debugger (GDB)                             | 81  |

|   |      | 3.6.2     | Intel Debugger (IDB)                           | 82  |

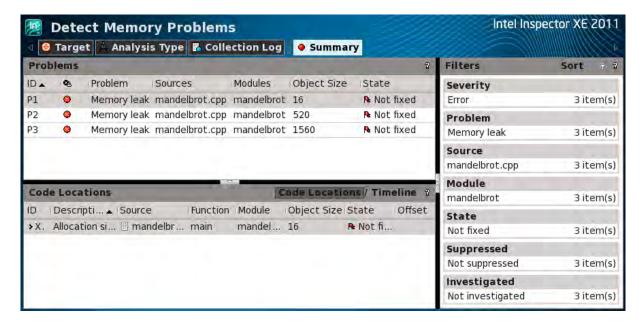

|   |      | 3.6.3     | Intel Inspector XE 2011                        | 82  |

|   |      | 3.6.4     | GNU Profiler (gprof)                           | 83  |

|   |      | 3.6.5     | OProfile                                       | 85  |

|   |      | 3.6.6     | Valgrind                                       | 85  |

|   |      | 3.6.7     | AMD CodeAnalyst for Linux                      | 87  |

|   |      | 3.6.8     | Intel VTune Amplifier XE 2011 for Linux        | 88  |

| 4 | Para | illel Pro | ogramming Techniques                           | 90  |

|   | 4.1  | Introdu   | uction                                         | 90  |

|   | 4.2  | Perform   | mance Analysis and Tuning                      | 90  |

|   | 4.3  | The Tu    | uning Process                                  | 91  |

|   | 4.4  | Seque     | ntial Optimisations                            | 93  |

|   |      | 4.4.1     | Loop Optimisations                             | 94  |

|   |      | 4.4.2     | Aligning, Padding, and Sorting Data Structures | 99  |

|   |      | 4.4.3     | Avoid Branching                                | 100 |

|   |      | 4.4.4     | Vectorisation                                  | 100 |

*CONTENTS* iv

|   | 4.5   | Paralle                       | el Programming Patterns                | 01                   |

|---|-------|-------------------------------|----------------------------------------|----------------------|

|   |       | 4.5.1                         | Identifying Concurrency                | 02                   |

|   |       | 4.5.2                         | Algorithm Structure                    | 05                   |

|   |       | 4.5.3                         | Supporting Structures                  | .08                  |

|   |       | 4.5.4                         | Implementation Mechanisms              | 10                   |

|   | 4.6   | Paralle                       | el Optimisations                       | 11                   |

|   |       | 4.6.1                         | Data Sharing                           | 12                   |

|   |       | 4.6.2                         | Reduce Lock Contention                 | 12                   |

|   |       | 4.6.3                         | Load Balancing                         | 14                   |

| _ | M 041 | ا ما ما ما                    |                                        | 16                   |

| 5 |       | hodolog                       | עס                                     |                      |

|   | 5.1   |                               | rch Design                             |                      |

|   | 5.2   | Systen                        | n Specifications and Software Versions | 17                   |

|   | 5.3   | Autom                         | nated Benchmarking Tool                | 18                   |

|   |       | 5.3.1                         | Extensions to the Benchmarking Tool    | 19                   |

| 6 | Imp   | lementa                       | ation 1                                | 20                   |

|   | 6.1   | Introdu                       | uction                                 | 20                   |

|   | 6.2   | Matrix                        | Multiplication                         | 21                   |

|   |       | 6.2.1                         | Initial Profiling and Analysis         | 21                   |

|   |       | 6.2.2                         | Sequential Optimisations               | 22                   |

|   |       |                               | 1 1                                    |                      |

|   |       | 6.2.3                         | Parallel Implementations               | 24                   |

|   | 6.3   |                               |                                        |                      |

|   | 6.3   |                               | Parallel Implementations               | 32                   |

|   | 6.3   | Mande                         | Parallel Implementations               | .32                  |

|   | 6.3   | Mande 6.3.1                   | Parallel Implementations               | 32<br>32<br>34       |

|   | 6.3   | Mande 6.3.1 6.3.2 6.3.3       | Parallel Implementations               | 32<br>32<br>34<br>37 |

|   |       | Mande 6.3.1 6.3.2 6.3.3       | Parallel Implementations               | 32<br>34<br>37<br>54 |

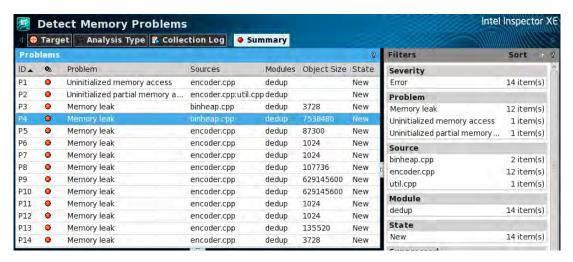

|   |       | Mande 6.3.1 6.3.2 6.3.3 Dedup | Parallel Implementations               | 32<br>34<br>37<br>54 |

*CONTENTS* v

| 7 | Resu | ılts      |                         | 171   |

|---|------|-----------|-------------------------|-------|

|   | 7.1  | Matrix    | Multiplication          | . 173 |

|   |      | 7.1.1     | Runtime Performance     | . 173 |

|   |      | 7.1.2     | Code Metrics            | . 176 |

|   |      | 7.1.3     | Discussion              | . 176 |

|   | 7.2  | Mande     | elbrot Set Algorithm    | . 178 |

|   |      | 7.2.1     | Runtime Performance     | . 178 |

|   |      | 7.2.2     | Code Metrics            | . 182 |

|   |      | 7.2.3     | Discussion              | . 182 |

|   | 7.3  | Dedup     | Kernel                  | . 184 |

|   |      | 7.3.1     | Runtime Performance     | . 184 |

|   |      | 7.3.2     | Code Metrics            | . 188 |

|   |      | 7.3.3     | Discussion              | . 188 |

|   |      | 7.3.4     | Overall Findings        | . 189 |

| 8 | Con  | clusion   |                         | 192   |

| A | Rele | evant Co  | ompiler Options         | 207   |

|   | A.1  | GNU (     | C/C++ Compiler          | . 207 |

|   | A.2  | Intel C   | and C++ Compilers       | . 209 |

| В | Base | eline Pr  | ogram Source Code       | 211   |

|   | B.1  | Matrix    | Multiplication          | . 211 |

|   | B.2  | Mande     | elbrot Set              | . 212 |

|   | B.3  | Dedup     | lication Kernel         | . 213 |

| C | Para | allelised | Program Source Code     | 224   |

|   | C.1  | Shared    | Task Queue for Pthreads | . 224 |

# **List of Figures**

| 2.1  | State transition diagram for process execution           | 8  |

|------|----------------------------------------------------------|----|

| 2.2  | Parallel execution through a critical section            | 9  |

| 2.3  | Deadlock between two threads                             | 11 |

| 2.4  | Speedup according to Amdahl's Law                        | 15 |

| 2.5  | Scaling according to Amdahl's Law and Gustafson's Law    | 17 |

| 2.6  | Components of a computer and the central processing unit | 22 |

| 2.7  | Flynn's Taxonomy                                         | 25 |

| 2.8  | Dual-core chip multiprocessor                            | 28 |

| 2.9  | Memory structure for cache memory                        | 34 |

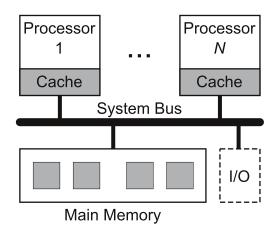

| 2.10 | UMA processor organisation                               | 38 |

| 2.11 | CC-NUMA processor organisation                           | 40 |

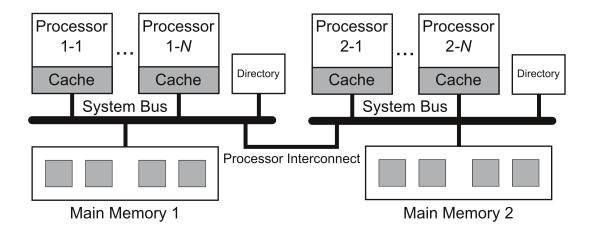

| 3.1  | The Eclipse CDT IDE                                      | 79 |

| 3.2  | The NetBeans C/C++ IDE                                   | 79 |

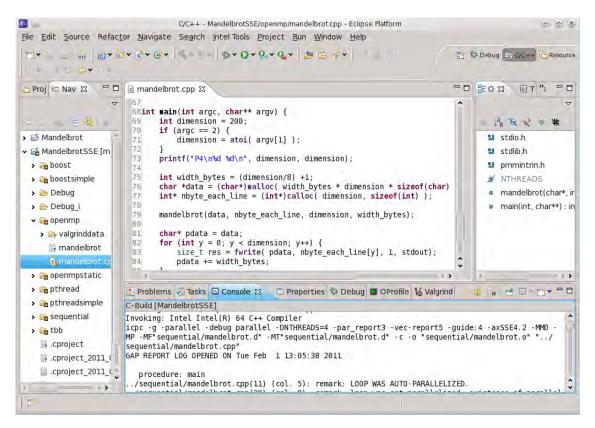

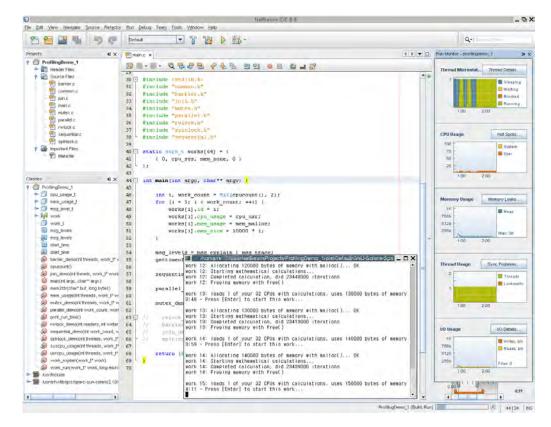

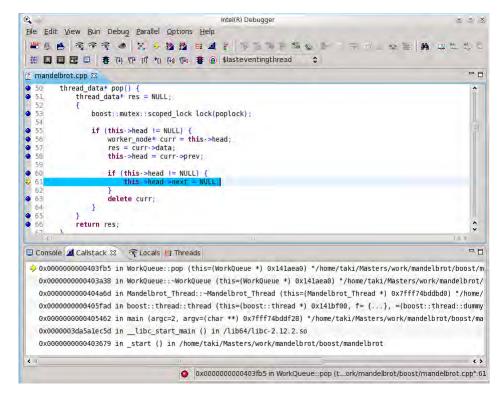

| 3.3  | Eclipse-based IDB user interface                         | 84 |

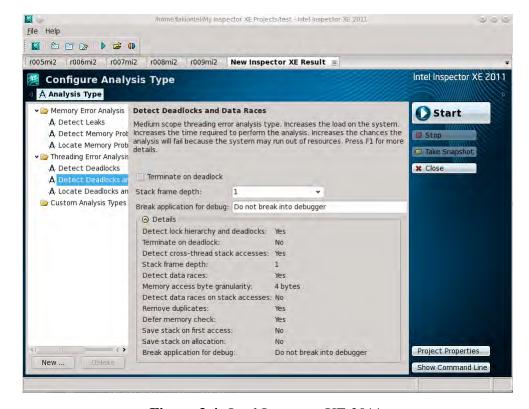

| 3.4  | Intel Inspector XE 2011                                  | 84 |

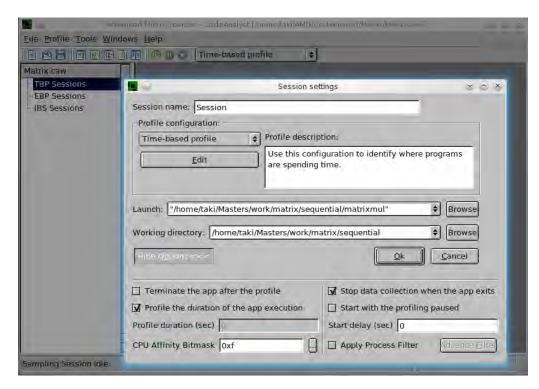

| 3.5  | AMD CodeAnalyst for Linux                                | 89 |

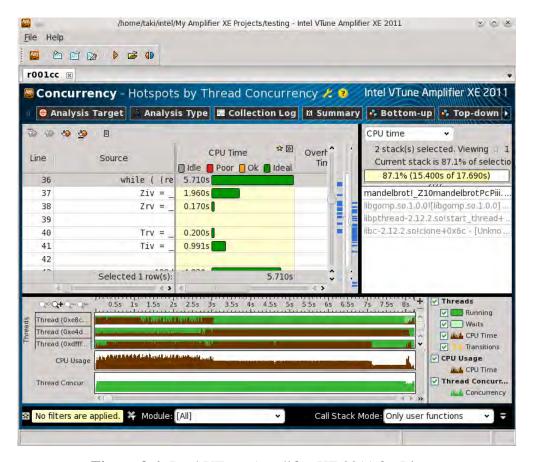

| 3.6  | Intel VTune for Linux                                    | 89 |

| 4.1  | Approach to performance analysis and tuning              | 93 |

LIST OF FIGURES vii

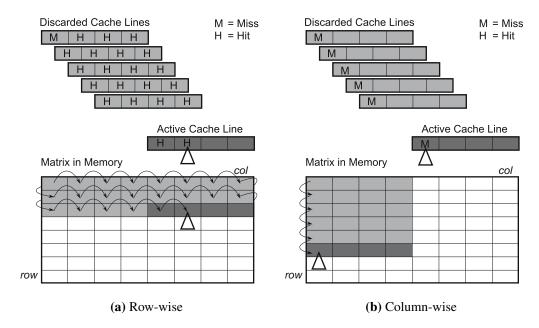

| 4.2 | Cache usage for row-wise and column-wise matrix access                             |

|-----|------------------------------------------------------------------------------------|

| 6.1 | Callgrind summary for unoptimised <b>mandelbrot</b> program                        |

| 6.2 | Callgrind summary for optimised <b>mandelbrot</b> program                          |

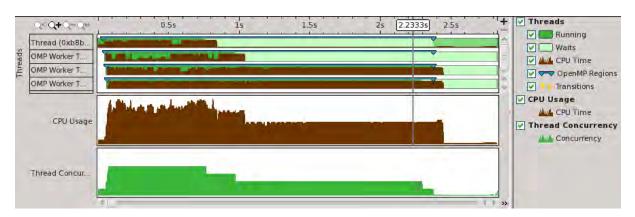

| 6.3 | VTune concurrency profiling for the statically scheduled OMP <b>mandelbrot</b> 140 |

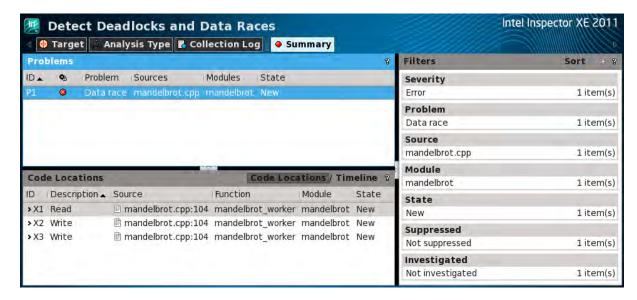

| 6.4 | Data race error detected by Intel Inspector in the shared task queue 144           |

| 6.5 | Memory leak detected by Intel Inspector in the shared task queue                   |

| 6.6 | VTune CPU usage summary for the statically scheduled Boost <b>mandelbrot</b> 153   |

| 6.7 | Memory errors detected by Intel Inspector in <b>dedup</b>                          |

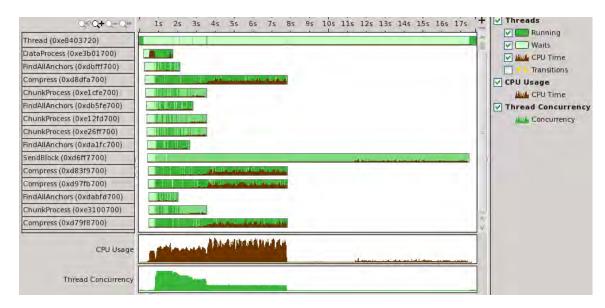

| 6.8 | VTune thread concurrency analysis of Pthreads <b>dedup</b>                         |

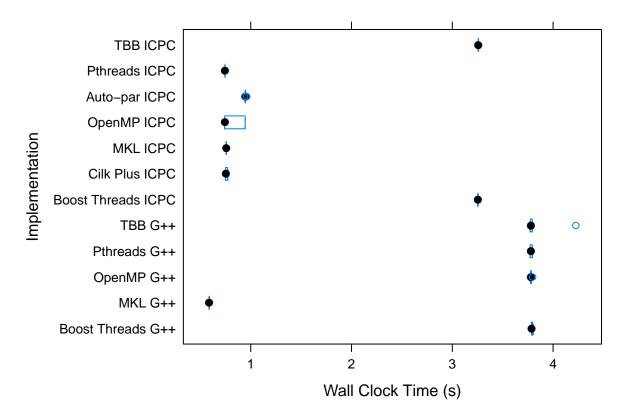

| 7.1 | Runtime performance for parallel implementations of <b>matrixmul</b> 173           |

| 7.1 | Runtime performance for paramet implementations of <b>matrixinu</b>                |

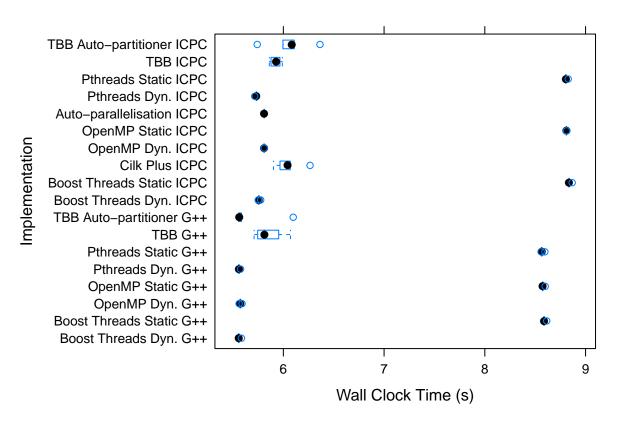

| 7.2 | Runtime performance for parallel implementations of <b>mandelbrot</b> 179          |

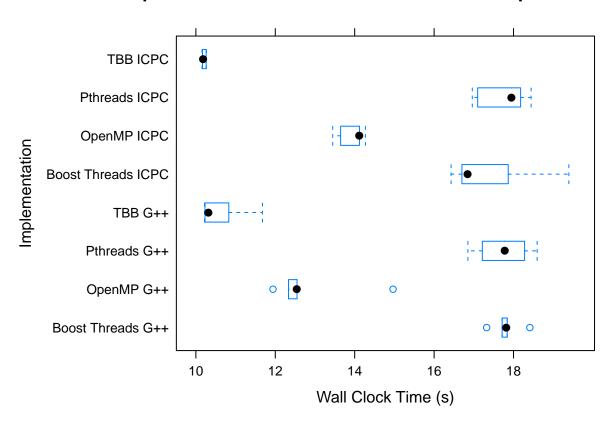

| 7.3 | Runtime performance for parallel implementations of <b>dedup</b>                   |

# **List of Tables**

| 2.1  | Race Condition between two threads                                                  | 10  |

|------|-------------------------------------------------------------------------------------|-----|

| 3.1  | Pthreads interface categories                                                       | 60  |

| 3.2  | Clauses for OpenMP directives                                                       | 68  |

| 4.1  | Loop interchange performance summary                                                | 95  |

| 5.1  | System hardware specifications                                                      | 118 |

| 5.2  | System software specifications                                                      | 118 |

| 6.1  | Performance of the original, unoptimised sequential <b>matrixmul</b> program        | 122 |

| 6.2  | Performance of <b>matrixmul</b> with sequential optimisations                       | 122 |

| 6.3  | Performance of <b>matrixmul</b> with improved array access                          | 123 |

| 6.4  | Performance of <b>matrixmul</b> with interprocedural optimisations                  | 123 |

| 6.5  | Performance of <b>matrixmul</b> with automatic parallelisation and vectorisation    | 125 |

| 6.6  | Performance of OpenMP matrixmul with and without automatic vectorisation            | 126 |

| 6.7  | Performance of TBB <b>matrixmul</b> with and without automatic vectorisation        | 127 |

| 6.8  | Performance of Pthreads <b>matrixmul</b> with and without automatic vectorisation . | 128 |

| 6.9  | Performance of Boost <b>matrixmul</b> with and without automatic vectorisation      | 129 |

| 6.10 | Performance of Cilk Plus <b>matrixmul</b> with and without automatic vectorisation  | 130 |

| 6.11 | Performance of MKL matrixmul with and without automatic vectorisation               | 131 |

| 6.12 | Performance of the original, unoptimised <b>mandelbrot</b> program                  | 134 |

LIST OF TABLES ix

| 6.13 | Performance of <b>mandelbrot</b> with sequential optimisations                                       | 134 |

|------|------------------------------------------------------------------------------------------------------|-----|

| 6.14 | Performance of <b>mandelbrot</b> with IPO and PGO compiler optimisations                             | 134 |

| 6.15 | Performance of <b>mandelbrot</b> with SSE vectorisation                                              | 137 |

| 6.16 | Performance of auto-parallelised <b>mandelbrot</b>                                                   | 139 |

| 6.17 | Performance of OMP mandelbrot with static and dynamic scheduling                                     | 140 |

| 6.18 | Performance of TBB <b>mandelbrot</b> with and without the auto-partitioner                           | 142 |

| 6.19 | Performance of Cilk Plus mandelbrot                                                                  | 143 |

| 6.20 | Performance of Pthreads <b>mandelbrot</b> with static and dynamic scheduling                         | 149 |

| 6.21 | Performance of Boost mandelbrot with static and dynamic scheduling                                   | 153 |

| 6.22 | Performance of the original, unoptimised sequential <b>dedup</b> program                             | 156 |

| 6.23 | Performance of <b>dedup</b> with increasing compiler optimisation levels                             | 157 |

| 6.24 | Performance of <b>dedup</b> with interprocedural and profile-guided optimisations .                  | 157 |

| 6.25 | Performance of Pthreads <b>dedup</b> implementation                                                  | 162 |

| 6.26 | Performance of Boost Threads <b>dedup</b> implementation                                             | 165 |

| 6.27 | Performance of OpenMP <b>dedup</b> implementation                                                    | 168 |

| 6.28 | Performance of TBB <b>dedup</b> implementation                                                       | 170 |

| 7.1  | Performance of compiler optimisations for sequential <b>matrixmul</b> program                        | 174 |

| 7.2  | Performance of parallel <b>matrixmul</b> implementations                                             | 175 |

| 7.3  | Static code metrics for the implementations of the <b>matrixmul</b> program                          | 176 |

| 7.4  | Performance of compiler optimisations for sequential <b>mandelbrot</b> program                       | 180 |

| 7.5  | Performance of parallel mandelbrot implementations                                                   | 181 |

| 7.6  | Static code metrics for the implementations of the <b>mandelbrot</b> program                         | 182 |

| 7.7  | Performance of compiler optimisations for sequential <b>dedup</b> program                            | 186 |

| 7.8  | Performance of parallel <b>dedup</b> implementations                                                 | 187 |

| 7.9  | Static code metrics for the implementations of the <b>dedup</b> program                              | 188 |

| 7.10 | Performance to Effort ratio calculations for <b>matrixmul</b> , <b>mandelbrot</b> , and <b>dedup</b> | 191 |

# Listings

| 2.1  | Pseudocode example of a critical section                        |

|------|-----------------------------------------------------------------|

| 3.1  | Simple Pthreads example                                         |

| 3.2  | Simple Boost Threads example                                    |

| 3.3  | Short TBB parallel program example                              |

| 3.4  | Short OpenMP parallel program example                           |

| 3.5  | Cilk Plus parallel quicksort example                            |

| 3.6  | Cilk Plus array notation and elemental functions                |

| 6.1  | Classic matrix multiplication algorithm                         |

| 6.2  | Matrixmul with improved array access pattern                    |

| 6.3  | Parallel matrix multiplication using OpenMP                     |

| 6.4  | Parallel matrix multiplication using Thread Building Blocks     |

| 6.5  | Parallel matrix multiplication using Pthreads                   |

| 6.6  | Parallel matrix multiplication using Boost Threads              |

| 6.7  | Parallel matrix multiplication using Cilk Plus                  |

| 6.8  | Parallel matrix multiplication using MKL                        |

| 6.9  | Escape time Mandelbrot set algorithm                            |

| 6.10 | Vectorised Mandelbrot set algorithm                             |

| 6.11 | Parallel <b>mandelbrot</b> using OpenMP with static scheduling  |

| 6.12 | Parallel <b>mandelbrot</b> using OpenMP with dynamic scheduling |

| 6.13 | TBB parallel for implementation with MandelPar class            |

*LISTINGS* xi

| 6.14 | Cilk Plus mandelbrot implementation                                      | 142 |

|------|--------------------------------------------------------------------------|-----|

| 6.15 | Shared task queue data structure for dynamic scheduling                  | 145 |

| 6.16 | Protecting concurrent access to the task queue using Pthreads mutex      | 145 |

| 6.17 | Protecting concurrent access to the task queue using Boost Threads locks | 146 |

| 6.18 | Pthreads mandelbrot main function using static scheduling                | 147 |

| 6.19 | Pthreads mandelbrot_worker function using static scheduling              | 148 |

| 6.20 | Pthreads mandelbrot main function using dynamic scheduling               | 148 |

| 6.21 | Pthreads mandelbrot_worker function using dynamic scheduling             | 149 |

| 6.22 | Boost Threads mandelbrot main function with static scheduling            | 150 |

| 6.23 | Boost Threads Mandelbrot_Thread class with static scheduling             | 151 |

| 6.24 | Boost Threads mandelbrot main function with dynamic scheduling           | 151 |

| 6.25 | Boost Threads Mandelbrot_Thread class with dynamic scheduling            | 152 |

| 6.26 | Deduplication encoding function                                          | 155 |

| 6.27 | Encoding function for parallel <b>dedup</b> using Pthreads               | 160 |

| 6.28 | Thread-safe queue using Pthreads mutexes and condition variables         | 162 |

| 6.29 | Encoding function for parallel <b>dedup</b> using Boost Threads          | 164 |

| 6.30 | Thread-safe queue using Boost Threads mutexes and condition variables    | 165 |

| 6.31 | Encoding function for parallel <b>dedup</b> using OpenMP                 | 166 |

| 6.32 | Thread-safe queue using OpenMP locks                                     | 167 |

| 6.33 | Encoding function for parallel <b>dedup</b> using TBB                    | 168 |

| 6.34 | ChunkProcess filter class for parallel <b>dedup</b> using TBB            | 169 |

| B.1  | Classic matrix multiplication program                                    | 211 |

| B.2  | Mandelbrot Set program                                                   | 212 |

| B.3  | Deduplication serial encoding pipeline                                   | 213 |

| C.1  | Shared Task Queue using Pthreads mutex                                   | 224 |

### Chapter 1

### Introduction

With the advent of commercial multicore processors, modern computer systems have taken on parallel capabilities. It is now common for modern commodity computer systems to ship with two or more processor cores and the chip manufacturers are not stopping there [19, 124]. CPUs with between two and twelve physical processor cores are readily available from manufacturers such as AMD, IBM, Intel, and Oracle Sun, with sixteen-core variants on the near horizon. The Sun SPARC T-series, IBM POWER7, and Intel Hyper-Threading enabled range of processors take multicore parallel processing a step further by supporting multiple threads of execution per core. Intel's Tera-scale research program has even produced 48-core and 80core experimental CPUs for research purposes, demonstrating the potential for highly parallel manycore architectures [62, 94, 132]. These multicore and multiprocessor computer systems are seeing use almost everywhere, particularly in the server and workstation markets, as well as in scientific computing where hundreds of multicore CPUs are harnessed to form massively parallel supercomputers. This trend towards increasing the number of processor cores instead of improving clock speeds can be attributed to the physical limitations of modern processor designs [54, 53, 124, 136]. Other processor improvements, such as instruction-level parallelism, are also reaching their limits and it is becoming harder for CPU designers to increase the performance of the individual processor cores. As such, multicore designs represent both the present and future of the CPU and signal the need for programmers to start thinking in parallel as opposed to the traditional sequential programming model [54, 136].

This has serious implications for the design and development of applications, since writing and debugging parallel software is a difficult task that requires more knowledge and expertise than sequential programming [53, 136, 141]. So, following the commitment of chip manufacturers to the development of multicore CPUs, the key limiting factors for software performance are the

parallel programming abilities of software programmers and the availability of easy-to-use, efficient parallel programming models and parallel-aware software development tools. However, well over a hundred different parallel programming models and libraries have been developed over the years, most of which failed to gain any traction in the programming community, leaving only a handful still in widespread use. Therefore, programmers and library developers should focus on using and extending the current range of successful parallel programming models instead of attempting to develop new models that may only see limited use. The real problem lies in helping programmers to think in parallel and providing methodical approaches to identifying and exploiting the potential parallelism in a program using an appropriate parallel API or library [21, 102, 103, 141]. Further assistance is required when it comes to identifying and debugging errors and performance issues in the resulting parallel code. This is where parallelaware software development tools can come to the aid of the programmer [124]. A wide range of both free and commercial debugging and performance analysis tools are available, so the main problem lies in choosing the appropriate tools and learning how to use them effectively. Unfortunately, simply understanding the tools and methodologies for parallel programming is not enough to ensure that the resulting parallel program has good efficiency. The programmer also needs to understand the underlying platforms and architectures as they define a number of factors that affect performance, such as the importance of using cache to reduce memory access latency. The end result is that parallel programming requires more effort than sequential programming, so, where possible, parallel programming environments should attempt to reduce the effort required to develop correct efficient parallel programs [136].

There are several studies into the performance of parallel programs using various parallel programming models [6, 86, 87, 91, 14]. However, these studies tend to focus on the performance aspect and little attention is given to the quantitative analysis and comparison of the programming effort associated with implementing parallel programs using each of the selected parallel programming models. Kegel *et al.* [86, 87] present a subjective analysis of programming effort in respect to the parallel programming model, but very little work has gone into the quantitative analysis of performance versus programming effort.

#### 1.1 Problem Statement and Research Goals

The problem that we attempt to address in this thesis, either in full or in part, is the identification, selection, and usage of appropriate libraries, language extensions, tools, and approaches for the development of efficient parallel programs in C and C++ for the Linux platform from the standpoint of a novice parallel programmer, while minimising programmer effort. Our definition

of a novice parallel programmer primarily includes intermediate and advanced level sequential programmers starting to use parallel constructs. That being said, it is becoming increasingly important for those new to programming to be introduced to parallel programming concepts and the associated shift in the way of thinking about problems and their solutions.

This problem has a number of facets, which include the analysis of the hardware characteristics of multiprocessor systems, the identification of suitable parallel programming libraries and APIs, the identification of suitable parallel programming software development tools, implementing parallelism in several programs using each of the selected parallel programming models, measuring the performance of the implementations, measuring the code metrics associated with the implementations as an estimate of programming effort, and comparing the resulting measurements between the different parallel programming models.

Therefore, the research goals of this thesis are fourfold:

- 1. Describe the key concepts of parallel programming and provide an overview of the organisational and architectural characteristics of commodity multiprocessor computer systems as they relate to performance.

- 2. Provide a short survey of current parallel programming models and parallel-aware software development tools for C and C++.

- 3. Present and describe techniques for parallel programming and performance optimisation.

- 4. Evaluate and compare the performance and programming effort of several parallel program implementations using the different parallel programming models.

#### 1.2 Thesis Organisation

The relevant chapters of the thesis are organised as described below:

- **Chapter 2** introduces and discusses several important concepts related to multiprocessor computers and parallel programming.

- **Chapter 3** presents a short survey of common parallel programming models and libraries, as well as a variety of programming tools.

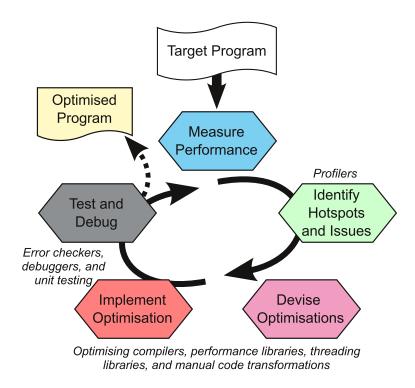

- **Chapter 4** describes a methodical approach to performance tuning, lists and describes a number of performance optimisations, and describes an approach to parallel programming using patterns.

- **Chapter 5** defines the research methodology for the empirical investigation and comparison of several parallel programming models.

- **Chapter 6** then describes the implementation of optimisations and parallelism in selected programs using the parallel programming models.

- **Chapter 7** presents, compares, and discusses the performance results and code metrics for the various implementations.

- **Chapter 8** summarises this thesis and presents the conclusions drawn from the research.

- **Appendix A** lists a selection of relevant compiler options, while **Appendix B** provides the code listings for the original sequential programs.

# Chapter 2

# **Background Work**

#### 2.1 Introduction

The field of concurrent and parallel computing has developed extensively over the last few decades, evolving from the early parallel supercomputers and mainframes to the modern massively parallel supercomputers and commodity parallel processors commonly found in desktops, servers, laptops, and even gaming consoles. The software driving these systems has also progressed substantially, resulting in a myriad of concurrent and parallel programming models and systems. Understanding these systems and the underlying hardware is critical, as so aptly stated by Herlihy and Shavit in the quote below.

You cannot program a multiprocessor effectively unless you know what a multiprocessor *is*. [56, p. 469]

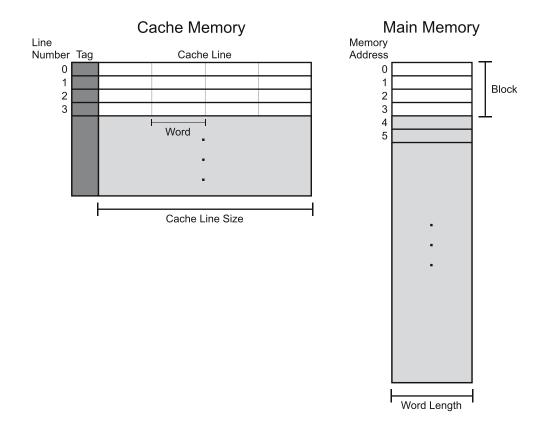

In this chapter, we present the main concepts associated with parallel computing as they pertain to later discussions. We also present a brief introduction to computer organisation, focusing on processor and memory organisations typically found in modern commodity computer hardware, since the programmer can often leverage the characteristics of the hardware to improve the performance of the target program. This is particularly evident with memory and cache systems, where the understanding and effective use of the caching mechanism can improve performance significantly.

Furthermore, we describe the performance characteristics of parallel programs and how these metrics and models can be used to determine the efficiency of parallel algorithms and programs on increasingly parallel computer systems. In addition to these performance metrics,

we describe a number of code metrics that measure or model the complexity of program code. These code metrics are used in the evaluation as a way of defining the effort expended by the programmer.

### 2.2 Parallel Programming Terms and Concepts

To avoid any ambiguity or misunderstanding, we first present our definitions for some of the key terms and concepts as used in this thesis.

#### 2.2.1 Serial Computing

Serial or *sequential computing* essentially follows the von Neumann architecture, whereby a single *central processing unit (CPU)* executes a program stored in memory that specifies a sequence of read and write operations on that memory [11, 35, 115]. The problem is broken into a sequence of instructions or operations, which perform the computations necessary to solve the problem. These operations execute one after another (in other words, sequentially), with only one instruction being executed at any one time [11].

Modern CPUs and operating systems distort this description somewhat, introducing an element of concurrency to otherwise sequential programs. Hardware level improvements in modern CPUs allow for instruction-level parallelism as described in Section 2.4.1. *Multitasking* operating systems interleave the execution of multiple programs on a computer with a single processor using mechanisms such as *time-slicing*, thereby giving the illusion of parallelism [99, 103]. Serial programs that are written to be executed on a single processor, can typically run on parallel computers without modification. However, this does not mean that the program will execute in parallel, or that the program will execute exclusively on one processor as the operating system may schedule execution over different processors during the program's lifetime.

#### 2.2.2 Parallel Computing

Parallel computing or parallel processing refers to the simultaneous execution of computational tasks over multiple processors to solve the specified problem [11]. This is similar to concurrency, but there is a subtle distinction between concurrency and parallel execution. Concurrency refers to the potential for simultaneous execution of independent computations within

a program. The *exploitable concurrency* is the degree to which it is possible to structure the code such that it harnesses or exploits the available concurrency [102].

A programmer harnesses this exploitable concurrency by breaking the problem down into discrete concurrent parts, and then developing and implementing a parallel algorithm using an appropriate parallel programming language or environment. When the resulting parallel program is executed on a parallel system, it is said to be executing in parallel if the instructions of concurrent computations are being executed on multiple different processors at the same time, as opposed to interleaving the execution of these concurrent instructions [11, 102]. The parallel system in question could be a single computer with multiple CPUs or processor cores, or it could be a cluster of computers connected by a network (*distributed processing*). It could even be a hybrid system where there is a cluster of multiprocessor computers [11, 99]. Parallel processing harnesses the exploitable concurrency in various problems to solve these problems in a shorter time or to solve bigger problem sets using more processors [11].

#### **2.2.3** Tasks

For our purposes, a *task* is defined as a chunk of work or sequence of instructions that needs to be processed or executed. The task itself is defined by the programmer and corresponds to the algorithm being implemented [102, 125]. It is also important to note that tasks are not explicitly associated with any particular *thread* or *unit of execution (UE)* until runtime.

#### 2.2.4 Processes and Threads

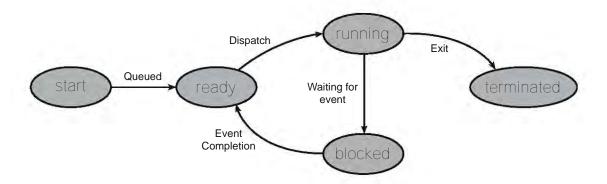

A *process* is a collection of resources and state, controlled by the operating system (OS). These resources include the input/output (I/O) descriptors or handles, security attributes, context information, and memory resources, including the runtime or call stack, heap, executable code and program data [99, 102, 131]. The state transitions for an executing process can be seen in Figure 2.1 [99, 131].

A *thread* can be seen as a distinct execution path within a process, with its own *instruction* pointer and stack and the ability to access shared memory between other threads within the process [102, 125].

In a multitasking operating system, the CPU scheduler allocates and de-allocates processor execution time for threads and processes using a *context switch* [99]. A thread or process can also

Figure 2.1: State transition diagram for process execution [99, 131].

be referred to generically as a unit of execution (UE). A process is considered a "heavyweight" UE, whereas threads are "lightweight" since they share the context of their parent process and thus have a lower context switching time [102].

#### **2.2.5** Locks

A *lock* or *mutual exclusion lock* (*mutex*) is a special shared variable or abstract data type that simplistically has two states: locked and unlocked. It also has methods for locking and unlocking the object. When a thread calls the lock method for a particular mutex, the state of the mutex is checked. If the mutex is currently locked (the lock has already been acquired by another thread), the calling thread will typically *spin* or *block* until the lock becomes available, otherwise it will immediately acquire the lock and continue execution. The unlock method simply releases the lock on the mutex and makes it available to other threads [20, 56, 124].

A *semaphore* is slightly different to a mutex in that it is used to constrain access to a shared resource instead of preventing simulataneous execution by multiple threads. The semaphore keeps track of resource accesses using an integer counter that is decremented on access to the resource and incremented once a thread is done using the resource. If the counter reaches zero, threads wanting to gain access to the resource will have to spin or block until the counter is greater than zero [20, 124]. An extended description of the various types of locks can be found in Section 2.5.

#### 2.2.6 Critical Sections, Barriers and Synchronisation

A *critical section* (CS) is a section of code that can only be executed by a single thread at any one time. This section is usually controlled by locking a critical section specific mutex and then

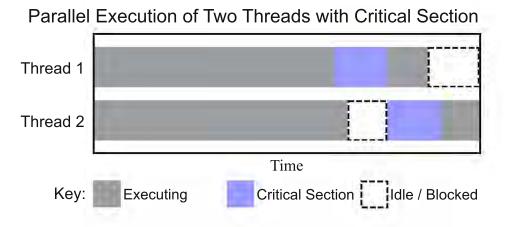

**Figure 2.2:** Parallel execution of two threads encountering a critical section.

unlocking the mutex at the end of the section. This prevents other threads from entering the critical section as they will block or spin while the mutex is locked. The use of mutexes and semaphores to protect critical sections forms the basis of mutual exclusion and synchronisation in parallel programming [20, 56, 99, 125].

The pseudocode example in Listing 2.1 shows a parallel max routine that makes use of a critical section to protect access to a global variable. Figure 2.2 shows the execution of threads encountering a critical section and demonstrates how threads block when they reach a critical section that is currently being traversed by another thread.

```

SET globalmax to 0

INIT maxmutex

SUBROUTINE parallel_max ARGS sublist

SET localmax to 0

FOR each element in the sublist

IF element > localmax THEN

STORE element in localmax

END IF

10

END FOR

/* start of critical section */

12

13

LOCK maxmutex

14

IF localmax > globalmax THEN

STORE localmax in globalmax

15

END IF

17

UNLOCK maxmutex

/* end of critical section */

18

END SUBROUTINE

```

**Listing 2.1:** Pseudocode example of a critical section.

Another important concept is that of a *barrier*, which is similar to a critical section except that instead of only letting one thread execute a particular section of code, the barrier forces

threads that reach it to wait or block until all threads in the group have reached that point. Once all the threads have reached the barrier, the blocked threads are notified that they may leave the barrier and continue executing [56, 105]. This is typically used in applications where progress on a new computation phase can continue only if the previous phase has been fully completed. Barriers essentially enforce synchronisation points for asynchronously executing groups of threads [56, 105].

#### 2.2.7 Race Conditions

A *data race condition* typically occurs when two or more threads attempt to update the same shared variable. The race condition becomes apparent when one thread overwrites the changes made by another thread, thus losing the original change and affecting the correctness of the program [20, 102, 125].

Consider the following scenario. Thread A reads the value of variable x with the intent of adding 5 to the existing value and saving the result back to x. Thread B, however, also wishes to modify x by taking the current value and subtracting 3 before saving the result back to x. If Thread B happens to read the value of x after Thread A reads it, but before Thread A stores the new value, a race condition occurs as the modification made by Thread A will be overwritten when Thread B stores its result [125]. The effect of this can be seen in Table 2.1. This is typically resolved by placing the code that modifies x within a critical section [20, 125].

**Table 2.1:** Race Condition between two executing threads [125].

| Thread A        | Thread B        | Х  |

|-----------------|-----------------|----|

| Read x: 7       | -               | 7  |

| -               | Read x: 7       | 7  |

| -               | Subtract 3      | 7  |

| Add 5           | -               | 7  |

| Update x: 7 + 5 | -               | 12 |

| -               | Update x: 7 - 3 | 4  |

Race conditions arise due to variable thread scheduling where the OS is responsible for the allocation and timing of thread execution as opposed to the programmer [102, 125]. This can lead to unpredictable and often hard to reproduce errors when modifying shared variables. Since the error may not present itself during testing, it often goes unnoticed until it affects the program in its production environment. Even if the error does get noticed, debugging is frustrated by the fact that thread execution is nondeterministic between program runs, which makes reproducing the problem particularly difficult. Errors of this nature are prevented by carefully implementing

**Figure 2.3:** Deadlock between two executing threads. Thread 1 acquires Lock A and Thread 2 acquires Lock B. Thread 1 then attempts to acquire Lock B and Thread 2 attempts to acquire Lock A, however, both locks have already been taken, resulting in a deadlock.

and controlling access to shared variables, using mutual exclusion and synchronisation where necessary [20, 102, 125].

#### 2.2.8 Deadlock

*Deadlock* occurs when at least two threads block indefinitely because they are each waiting for locks to be released that are currently being held by the other. This deadlocked state between threads results in the program never running to completion unless the deadlock is forcibly broken [20, 22, 102, 125].

If none of the threads gives up its currently held lock to allow another thread to continue, the threads will remain blocked forever as illustrated in Figure 2.3. When implementing mutual exclusion using locks, the programmer must take care to avoid implementing the locks such that deadlock can occur. One way that this can be done is by ensuring that locks are acquired in a specific order and by releasing currently held locks if all the necessary locks cannot be acquired at once and then trying again [20, 22].

Deadlock-freedom is the property whereby if some thread tries to acquire a lock, then some thread will succeed in acquiring the lock [56].

#### 2.2.9 Starvation and Livelock

Starvation is a condition whereby a thread is unable to progress because it is unable to gain access to required shared resources, which are protected by a critical section. This is typically caused by other threads monopolising access to the shared resource for extended periods of time [96, 109]. Should the thread in question regain access to the required shared resources, it will continue executing normally. Starvation-freedom is the property of a program whereby if a thread reaches a critical section, that thread will eventually execute its critical section [20, 7]. Starvation-freedom implies deadlock-freedom [56].

Livelock is a form of starvation whereby threads are unable to progress and perform useful work because they, or a required resource, are too busy servicing interrupts and requests from other threads [96, 109]. This is unlike deadlock, where the offending threads are mutually blocking each other, in that the program can recover if the interrupts or requests decrease to a point where the thread can progress with useful work. Livelock-freedom is a weaker property, compared to starvation-freedom, and states that if a thread reaches a critical section, then some thread eventually executes its critical section [20, 7].

#### 2.3 Parallel Performance

As with most performance improvement efforts, the ultimate goal is to improve speedup and scalability. These performance characteristics can be predicted using models or measured in practice. Some common performance measures are defined below.

- **CPU time** is the sum of the time spent actively executing the instructions of a particular computer program for each processor [54].

- Wall clock time or *elapsed time* is the real-world execution time of a program, including overheads and input/output delays [54].

- Latency refers to time delay between the issuing of a request and the response to the request [54].

- **Throughput** is a measure of the amount of data transferred or requests serviced per unit of time [54].

While measuring the actual performance of the program in question provides the best indication of speedup and scalability issues, it is often useful to predict and anticipate these metrics with the aid of the models given below. *Amdahl's Law* and *Gustafson's Law* allow one to anticipate the speedup for future systems for which neither processor counts nor workload sizes are currently available, thus preventing direct measurement. These analytical models do not predict all aspects of parallel performance, but they do provide a base for expected performance. However, profiling is the only way to accurately identify the sections of code that will provide the greatest gain from optimisation.

#### 2.3.1 Speedup

When talking about speedup, the total running time to complete execution of the program (wall clock time) is typically taken as the primary metric. This total time is denoted by  $T_{total}(P)$ , where P represents the number of processors. The total time can often be decomposed into a number of *serial terms*, representing the portions of the program that cannot be run in parallel, and a compute portion, which can be distributed over as many processors as are available [102]. The serial terms usually consist of initialisation and finalisation routines that are unable to split their workload between additional processors. However, the compute portion of the program is able to execute its workload in parallel and is represented by the time to complete the compute portion on one processor over the number of available processors [102]. This relationship between the serial terms and the parallel compute section, resulting in the total time, can be seen in (2.1) [102].

$$T_{total}(P) = T_{initialisation} + \frac{T_{compute}(1)}{P} + T_{finalisation}$$

(2.1)

It must be noted that (2.1) only reflects the simplified case where there are no overheads such as thread startup and scheduling or locking, which affect the performance of the parallel compute section. However, this concept of serial and parallel sections of code is important and is reexamined in Section 2.3.2.

The *relative speedup* of a program, denoted by S and shown in (2.2), is another useful measure for parallel programming. It determines how much faster a particular program will run when additional processors are made available. It is calculated by dividing the total time for executing the program with one processor by the total time for P processors. While *perfect linear speedup*, where the speedup is equal to P, is the desired outcome, this is seldom possible as the serial terms are unable to execute faster with additional processors [102]. However, in some rare cases,

superlinear speedup can be achieved through efficient cache utilisation between processor cores on the same CPU, which overcomes the lack of speedup for the serial terms [21].

$$S(P) = \frac{T_{total}(1)}{T_{total}(P)}$$

(2.2)

Related to the concept of relative speedup is the measure for *efficiency*, denoted by E and shown in (2.3). Efficiency is simply the speedup of the program over the number of processors [102]. This measure is useful in that it provides an easier to understand measure for how effectively additional processors are utilised.

$$E(P) = \frac{T_{total}(1)}{PT_{total}(P)}$$

(2.3)

#### 2.3.2 Amdahl's Law

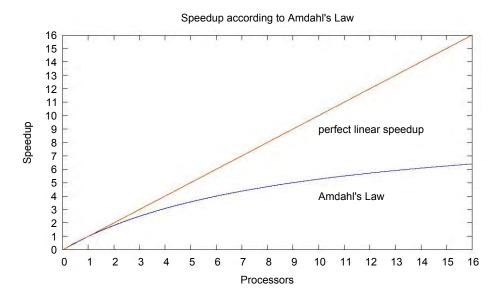

As previously described, parallel programs consist of both serial and parallel sections of code. A problem arises when one adds increasingly more processors in an attempt to improve the speedup of the program. As the processor count increases, so does the speedup, but not at the same rate. The problem lies with the well-known Amdahl's law, defined in (2.4).

$$S_{\text{AMDAHL}}(P) = \frac{1}{(1-f) + \frac{f}{P}},$$

(2.4)

where  $S_{\rm AMDAHL}$  represents the speedup, f the proportion of the program that executes in parallel, and P the number of processors [56, 102, 125, 134]. In essence, this law states that speedup is hampered by the sequential portion of the program. As an example, given f = 0.9 and P = 10, the maximum speedup is only around 5.26x, which is clearly not ideal. The speedup value predicted by Amdahl's Law is generally an upper bound on the speedup as overheads in the parallel algorithm are not factored into the calculation. However, as mentioned in Section 2.3.1, there are cases where effective caching of data and other factors such as better resource utilisation, can result in a speedup greater than that predicted by Amdahl's Law [21, 102].

Furthermore, we can calculate the maximum attainable speedup given an infinite number of processors and an ideal parallel algorithm using (2.5) [102].

$$S_{\text{MAX}} = \frac{1}{1 - f} \tag{2.5}$$

**Figure 2.4:** Speedup according to Amdahl's Law for f = 0.9

It is quite clear from Figure 2.4, which depicts the graph for (2.4) with increasing values of P against perfect linear speedup given f = 0.9, that there are diminishing returns to adding more processors in an attempt to solve a problem faster. Amdahl's Law represents *fixed-size speedup* and it is often considered a pessimistic outlook on parallelism [125, 134].

It is therefore crucial to make every effort to reduce the sequential portion in programs to help increase speedup [56]. However, code that works well with four processors may not scale with eight or even sixteen processor cores, so careful attention must also be paid to the implementation of the parallel algorithm and managing the associated overheads [19].

#### 2.3.3 Gustafson's Law

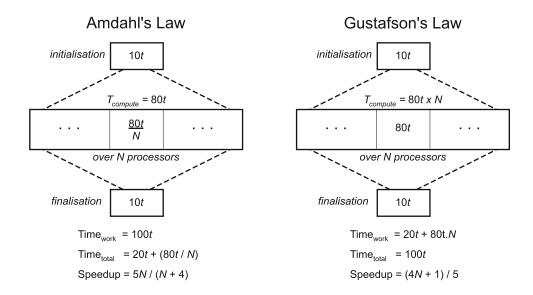

The problem with Amdahl's Law is that it focuses primarily on the speedup achieved when attempting to reduce the total runtime of a fixed workload by increasing the number of processors (fixed-size speedup). While this is the goal when implementing parallelism in many of the cases, John Gustafson re-evaluated Amdahl's Law and took another approach to achieving scalability with increasing hardware capabilities [102, 125, 134].

Gustafson considered the problem in a more positive light. He noted that if the proportion of the program that is sequential cannot be easily parallelised, better scaling can be achieved by performing more work in the parallel sections. The time spent in the serial portions of a program typically increase less than the parallel sections as the problem size or workload is increased,

thus reducing the serial fraction of the program. This is often referred to as *fixed-time scaling*. The reduction in the serial fraction with increasing problem size results in improved speedup and scaling as per Amdahl's Law [48, 102, 125]. Modern society's hunger for more information and the ever increasing volumes of data and information being produced by researchers and society alike play quite aptly into Gustafson's forward-thinking and optimistic approach to scaling [102]. However, not all problem sizes can be increased, so this approach may not always be applicable.

Returning to our earlier equations for total runtime and speedup, we can reformulate some of these terms and produce Gustafson's Law in terms of performance on a P-processor system [102]. First we define the *scaled serial fraction*, denoted by  $\gamma_{scaled}$  in (2.6), as the serial terms over the total time for P processors [102].

$$\gamma_{scaled} = \frac{T_{initialisation} + T_{finalisation}}{T_{total}(P)}$$

(2.6)

We derive the computation time on P processors in terms of the total time on P processors and the scaled serial fraction in (2.7).

$$T_{compute}(P) = T_{total}(P) - (T_{initialisation} + T_{finalisation})$$

$$= T_{total}(P) - \gamma_{scaled} T_{total}(P)$$

(2.7)

We then define the total time for one processor in terms of the parallel computation time and the serial terms for P processors, substituting in the equations from (2.6) and (2.7), to produce (2.8) [102]. Following on from this, we rewrite the equation for speedup as expressed in (2.2), taking into account the scaled serial portion and simplifying, which results in Gustafson's Law as defined in (2.9) [102].

$$T_{total}(1) = T_{initialisation} + PT_{compute}(P) + T_{finalisation}$$

$$= \gamma_{scaled}T_{total}(P) + P(T_{total}(P) - \gamma_{scaled}T_{total}(P))$$

$$= \gamma_{scaled}T_{total}(P) + P(1 - \gamma_{scaled})T_{total}(P)$$

(2.8)

Figure 2.5: Scaling according to Amdahl's Law and Gustafson's Law [125].

$$S_{\text{GUSTAFSON}}(P) = \frac{T_{total}(1)}{T_{total}(P)} = \frac{\gamma_{scaled} T_{total}(P) + P(1 - \gamma_{scaled}) T_{total}(P)}{T_{total}(P)}$$

$$= \gamma_{scaled} + P(1 - \gamma_{scaled})$$

$$= P + (1 - P)\gamma_{scaled}$$

(2.9)

An interesting observation can be made about the above equation. If the time taken by the serial terms remains constant and we keep the size of the computation for each processor the same, eventually we reach a point where the speedup increases at the same rate as the number of processors, which is known as *linear* or *order of n scaling* [125, 102].

The illustration in Figure 2.5 highlights the key difference between Amdahl's Law (fixed-time scaling) and Gustafson's observations (fixed-size scaling), showing that scaling can be improved by increasing the problem size. This ultimately results in far more effective use of the available processing power compared to a static workload [125]. Depicted in the illustration is a program with serial terms, which perform initialisation and finalisation, and a parallel computation section executing concurrently on N processors. Time taken for each section of work is represented in the arbitrary unit t, and summaries of total times and speedup (highlighting the speedup limitations of Amdahl's Law) are presented below each diagram.

Sun *et al.* [134] note that the *memory-wall problem*, referring to the performance gap between memory and processors, is likely to play a greater role in determining speedup in the future.

#### 2.3.4 Sequential Algorithms versus Parallel Algorithms

While Amdahl's Law and Gustafson's Law provide a means for us to predict speedup for programs running on a parallel system, they are based on the flawed assumption that the program must execute roughly the same number and type of instructions for both the serial and parallel versions. However, there are cases where simply adapting the original serial algorithm to work in parallel is inefficient and a more natural parallel implementation exists. In cases such as this, it is often worthwhile re-examining the problem and designing a more suitable parallel algorithm [125].

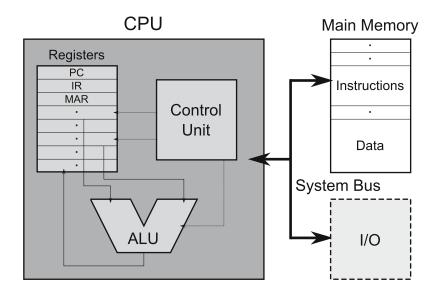

### 2.4 Computer Organisation

At a high level, a computer is made up of a number of components, namely, the central processing unit (CPU), memory (both primary and secondary storage memory), input and output (I/O) devices or components, and the interconnection structure between these components. The CPU executes the instructions that perform the operations necessary for the computer to function and carry out the given tasks. Computer memory is responsible for storing the instructions and data necessary for the operation of the computer. There are typically two kinds of memory: primary memories such as the RAM used by main memory and various caches; and the secondary or storage memory, which is used to store data on a more permanent basis [131]. I/O devices facilitate interaction between the computer and the user, through devices such as the keyboard and graphical display, or other devices and computers through components such as network interface cards (NIC) or serial ports. Finally, the interconnection network, typically in the form of a hierarchy of buses, is responsible for carrying address, control, and data signals between the various components in the system [131].

The performance of a computer depends on a multitude of factors, both hardware and software. Arguably, some of the greatest contributing factors are those pertaining to computer organisation for a given architecture. Organisational design choices such as the memory types, sizes, and hierarchy play an important role, especially given the widening gap between processor and memory performance [54, 131]. Our research focuses on software targeting commodity hardware and processors based on the x86 and x86-64 (64-bit) architectures, as these are the most common architectures due to their cost-effectiveness compared to larger specialised systems [27, 54]. As such, the computer organisation issues discussed in this section typically center around modern commodity hardware.

While at first, it may seem that these organisational factors only affect hardware designers and operating system programmers, many of them have consequences for application programmers in terms of how their programs are structured and coded. A good example of this is the effect on performance of good or bad cache utilisation, which can often be influenced by the programmer. As such, the key concepts regarding memory and processor organisation are presented below with particular emphasis on those factors affecting the programmer, or which can be influenced by the programmer in some manner.

#### 2.4.1 Processor Organisation

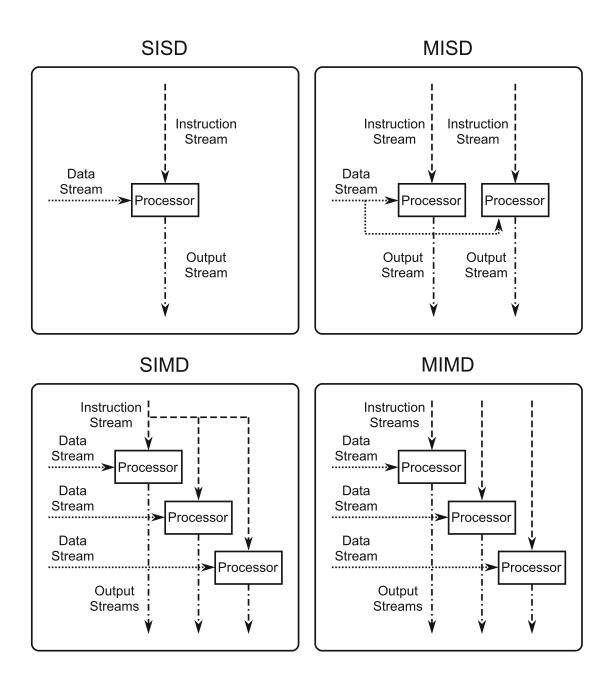

Processor organisation describes the characteristics of the processor and how one or more processors are connected to each other and to the rest of the system. In this section we briefly discuss the characteristics of modern CPUs and how they affect performance. We then go on to classify computer systems according to *Flynn's Taxonomy*, and describe common processor organisations for commodity hardware.

#### **CPU Characteristics**

The CPU or processor is central to the operation of a computer system. It is responsible for controlling the operations of the computer and executing instructions, thus enabling the computer to perform its allocated tasks [131]. The major components of a CPU in the von Neumann architecture, which paved the way for software in the form of stored programs, are described below and illustrated in Figure 2.6.

• Control Unit (CU): The control unit is responsible for fetching and interpreting instructions, and then issuing the necessary control signals to execute the instructions. Obtaining instructions and data from memory and then issuing control signals to general-purpose logic and arithmetic components to carry out those instructions gives these general-purpose processors the ability to execute instructions written by the programmer in the form of software programs. This is in contrast to hardwired programs where the logic components are designed and connected, at the hardware level, to take the input data and process it in a specific way. For such a system, changing the operation of the program requires that the hardware be rewired [131]. The architecture or instruction set of the processor determines the addressing modes and the types and formats of the instructions interpreted by

the control unit. Architectures fall into two broad categories: reduced instruction set computer (RISC) architectures, which are characterised by a large number of general-purpose registers and simple instruction sets with optimised instruction pipelines; or complex instruction set computer (CISC), architectures, which are characterised by a greater number of more complex and specialised instructions and fewer general-purpose registers [131].

The processing required to complete the *fetch cycle* and *execute cycle* for a single instruction, is known as an *instruction cycle*. The *interrupt cycle* must also be considered in this process. Devices and other components within the system can make *interrupt requests*, which are essentially events that cause the sequence of instructions for the current program to be suspended in order to service the appropriate interrupt handler instructions. After the interrupt has been dealt with, execution of the previously running program is automatically resumed [54, 131].

• **Registers:** The CPU contains a number of internal registers, which are a special type of memory or storage used to hold data that is necessary for the operation of the processor. The architecture of the processor determines the types and sizes of the registers that are implemented. For instance, a *stack-based* architecture arranges the registers to be accessed as a stack using Push and Pop instructions, whereas a *load-store* type of architecture will have a set of general-purpose registers that are accessed explicitly using Load and Store instructions [54].

As an example, a hypothetical *accumulator* architecture may have the following general-purpose registers: a *program counter* (*PC*), which tracks the address of the next instruction; an *instruction register* (*IR*), which holds the operation code or *opcode* for the current instruction; a *memory address register* (*MAR*), which holds the memory address to be read or written to; a *memory buffer register* (*MBR*) where the resulting data of the memory read is stored or where the data to be written is temporarily buffered; and an *accumulator* (*AC*), which holds the temporary results of operations performed by the ALU [131].

• Arithmetic and Logic Unit (ALU): The ALU performs the actual calculations and logic operations required to execute instructions. General-purpose arithmetic and logic components are found in the ALU and are configured to accept control signals from the control unit. The control signals specify how these components are combined so as to perform the desired operation. Some typical examples of arithmetic operations implemented in the ALU are the *add*, *subtract*, *multiply*, and *divide* operators. Integer and floating point data is treated differently, so there may be different implementations of these operators depending on the data type of the operands. Logic operations will typically include the *equal to*, *greater than*, and *less than* comparison operators, amongst others [131].

While the architecture prescribes which instructions need to be implemented, the manner in which these instructions are implemented is an organisational issue. It is up to the CPU designers to decide how the arithmetic and logic components are utilised to perform the required instructions. For example, the multiply operator can be implemented as a special multiply unit or the same effect can be achieved by using the add operator repeatedly [131]. These kinds of organisational design choices lead to CPUs within the same architecture family having different physical and performance characteristics.

• **CPU Interconnection:** An interconnection structure is needed to enable communication in the form of control, address, and data signals between the various components within the CPU as well as to the rest of the system. There are a variety of interconnection topologies including direct point-to-point, bus, hypercube, crossbar switch, mesh, ring, and torus. The bus interconnect is the most common structure for connecting the main system components. Hierarchies of buses are also typical in modern computer systems, with a local *front-side bus* on the CPU, which is connected to the system bus and lower buses, such as the expansion buses [115, 131]. Early processors used point-to-point links and buses internally, but crossbar switches, meshes, and ring networks have become common as well [54, 131]. The AMD Opteron range of CPUs support multiple Hyper-Transport links between CPU nodes in a multiprocessor system, which is based on the hypercube topology [27]. The torus, ring, and hypercube topologies are typically used to connect the nodes in supercomputers and clusters of computers [54, 124].

The performance of a bus or other interconnect is characterised by the *bandwidth* and *latency* of the interconnect, which are affected by the *bus width* and *frequency* of the connections. With regard to buses, bandwidth is typically understood to be the maximum rate of data or information transfer and can be measured in bits per second. Latency is the time it takes for a packet of information to complete its transmission between the source and destination [54, 115]. Bus width is the number of bits that can be transported over the bus in parallel, while frequency (clock frequency) is the number of cycles per second. The frequency and bus width are multiplied to produce the theoretical maximum bandwidth and in some cases, this can also be multiplied by the number of transfers per cycle for buses where multiple transfers per cycle are possible [131].

At the individual processor level, performance is determined by a number of factors, such as the *clock speed* or *clock frequency* and the number of *cycles per instruction* (CPI), although CPI is not directly comparable with other processors and instruction sets [54]. Instruction-level parallelism, as described in the next section, lowers the CPI by optimising the instruction pipeline and is critical to improving processor performance. The clock speed of a processor,

**Figure 2.6:** Components of a computer and the central processing unit in the von Neumann architecture [115, 54].

which is governed by a clock running at a constant rate, indicates the number of cycles executed per second by the processor. The clock speed is typically described by its rate (e.g., 2.4GHz, which is 2.4 billion cycles per second) [54]. Therefore, an increase in the clock speed of a processor results in more instructions executed per second and thus greater performance.

Historically, increases in processor performance have been brought about by increases in clock speed, along with incremental organisational improvements. This has been made possible by improvements in the fabrication process of integrated circuits, which have enabled the manufacturing of ever smaller electronic components, such as transistors. The reduced size of the components in turn, has allowed for these components to be packed more densely on a chip. This forms the basis of Moore's Law, derived from the observation by Gordon Moore, the cofounder of Intel, that the number of transistors that could be placed on a chip would double every year (this has recently slowed to doubling every 18 months) [53, 124, 131]. The so-called "scaling laws", observed by Robert Dennard and his colleagues at IBM, also derive from the *process shrink* in the manufacturing of chips. Dennard's first observation was that the voltage and current, and thus the power consumption of a transistor, is proportional to its area. This means that as these transistors get smaller and are placed more densely on a chip, the power density of the chip remains constant. The second observation was that the switching delay of a transistor is proportional to its size, and therefore the frequency or speed of the transistor increases as the transistor gets smaller [53].

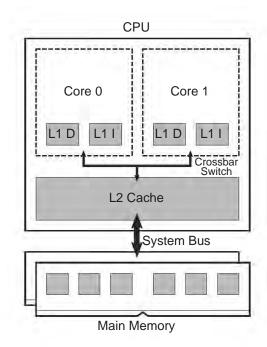

However, as the size of transistors decreases and the voltages are reduced, they begin to leak more current. Therefore, the voltage supplied to the transistors needs to be decreased at a lower rate than the decrease in transistor size to manage this leakage of current. This breaks the proportional power scaling and results in an increase in power density, which means that the chip produces more heat that needs to be dissipated in some way. Consequently, the frequency cannot be increased as easily because the voltage cannot be decreased and increasing the frequency without decreasing the voltage results in more heat. This places practical limits on the frequencies attainable by chips such as CPUs, based on how effectively the chips can be cooled [53, 124, 131]. It is for this reason that the manufacturers of modern commodity CPUs have turned to *multicore* designs. Since the number of transistors that can be packed on a chip is still increasing, it is possible to keep the processor frequency relatively constant and use the additional transistors to implement multiple processor cores on a single CPU package. This improves the performance of the CPU by adding parallel processing capabilities or *thread-level parallelism* [53, 54, 131].

#### **Instruction-Level Parallelism**

One particularly important organisational performance improvement is that of *pipelining*. As previously described, the instruction cycle consists of a fetch cycle and an execute cycle, which can be further broken down into a number of stages: fetching the instruction; decoding the instruction; calculating the addresses for operands and fetching them from memory; executing the instruction with the given operands; and finally storing the result back in memory. Without pipelining, the processor would have to wait for an instruction to pass through all of these stages before proceeding with the next instruction. However, with pipelining, it is possible to have multiple instructions in flight simultaneously, each at a different stage in the instruction cycle. This allows the processor to keep all stages of the instruction cycle busy, greatly improving performance [54, 82, 131]. Several conditions can affect the performance of pipelining due to *pipeline conflicts*, namely, resource conflicts, data dependencies, and conditional branch statements [54, 115]. Superpipelining extends this concept by adding a greater number of small stages, creating a deeper pipeline, which allows more instructions to be in the pipeline simultaneously [54, 82, 131].

Another important organisational improvement is the introduction of *superscalar* processors. In a superscalar processor, there are multiple instruction pipelines, which allows for independent instructions to be executed concurrently on a single processor [54, 82]. The goal of such processors is to enable the issuing of multiple instructions per clock cycle, resulting in a CPI value lower than one. These are also known as *multiple-issue processors* [54]. Both statically

and dynamically scheduled superscalar processors are available, with the Intel Itanium range being an example of statically scheduled superscalar processors, and the Intel Pentium range exhibiting dynamically scheduled superscalar features. Static scheduling relies on the compiler to schedule code for the processor and is typically characterised by *in-order* issuing and execution of instructions. Speculative dynamically scheduled superscalar processors, like the Intel Pentium 4, allow for *out-of-order* issuing and execution of instructions. Out-of-order execution with speculation means that the processor's scheduler is able to fetch, issue, and execute independent instructions from outside the normal, sequential instruction order, thus allowing for better utilisation of the multiple instruction pipelines [54]. This can be combined with pipelining or superpipelining, resulting in a *superpipelined superscalar processor*. Both pipelining and superscalar processors exhibit an *instruction-level parallelism* [131].