# Designing and implementing a new Pulsar Timer for the Hartebeesthoek Radio Astronomy Observatory.

A thesis submitted in fulfilment of the requirements for the degree of

### MASTER OF SCIENCE

of

### RHODES UNIVERSITY

by

## ANDREW DAVID YOUTHED

June 2007

#### Abstract

This thesis outlines the design and implementation of a single channel, dual polarization pulsar timing instrument for the Hartebeesthoek Radio Astronomy Observatory (HartRAO). The new timer is designed to be an improved, temporary replacement for the existing device which has been in operation for over 20 years. The existing device is no longer reliable and is difficult to maintain. The new pulsar timer is designed to provide improved functionality, higher sampling speed, greater pulse resolution, more flexibility and easier maintenance over the existing device. The new device is also designed to keeping changes to the observation system to a minimum until a full de-dispersion timer can be implemented at the observatory.

The design makes use of an 8-bit Reduced Instruction Set Computer (RISC) microprocessor with external Random Access Memory (RAM). The instrument includes an IEEE-488 subsystem for interfacing the pulsar timer to the observation computer system. The microcontroller software is written in assembler code to ensure optimal loop execution speed and deterministic code execution for the system.

The design path is discussed and problems encountered during the design process are highlighted. Final testing of the new instrument indicates an improvement in the sampling rate of 13.6 times and a significant reduction in 60Hz interference over the existing instrument.

#### ACKNOWLEDGEMENTS.

I would like to acknowledge the following people for their infinite help and undying patience:

- Mr. Richard Grant For his patience and help throughout this project as my supervisor. Corrections and silly questions included.

- Prof. Justin Jonas For his help and patience with all my silly questions on radio astronomy.

- Mr. Anthony Sullivan For his incredible patience and help during the design and implementation phases.

- Ms. Sarah Buchner For her help in rewriting the observing program for the new pulsar timer and providing most of the needed data after installation.

- Mr. Keith Jones For his help with ironing out the installation bugs in the new timer.

- The workshop crew at HartRAO For their incredible skills during the installation phase.

- The Hartebeesthoek Radio Astronomy Observatory For allowing me to work on such a great project and for all the financial help they provided.

- The Rhodes University Department of Physics & Electronics For helping make this project as pleasant as possible.

- My family For making this all possible with all the support one could hope for.

# Contents

| C             | onter | nts     | i                                             | ii             |

|---------------|-------|---------|-----------------------------------------------|----------------|

| Li            | st of | Figur   | es                                            | v              |

| $\mathbf{Li}$ | st of | Table   | s v                                           | ii             |

| 1             | Intr  | oduct   | ion                                           | 1              |

|               | 1.1   | What    | are pulsars?                                  | 1              |

|               | 1.2   |         | 1                                             | 2              |

|               | 1.3   |         |                                               | 3              |

| <b>2</b>      | Fun   | ctiona  | lity and technologies used                    | 6              |

|               | 2.1   | The fi  | inctionality of a period folding pulsar timer | 7              |

|               | 2.2   |         | · - · · ·                                     | 2              |

|               | 2.3   | -       | -                                             | 7              |

| 3             | The   | e new j | pulsar timer hardware 1                       | 9              |

|               | 3.1   | Comp    | onent selection                               | 20             |

|               |       | 3.1.1   | A/D components                                | 20             |

|               |       | 3.1.2   |                                               | 21             |

|               |       | 3.1.3   | Communications sub-system                     | 21             |

|               |       | 3.1.4   |                                               | 21             |

|               |       | 3.1.5   | Latch and divider                             | 22             |

|               |       | 3.1.6   | Microcontroller                               | 23             |

|               |       | 3.1.7   |                                               | 25             |

|               | 3.2   | Detail  | *                                             | 25             |

|               |       | 3.2.1   |                                               | 26             |

|               |       | 3.2.2   |                                               | 26             |

|               |       | 3.2.3   | LCD module                                    | 28             |

|               |       | 3.2.4   | Latch and divider module                      | 8              |

|               |       | 3.2.5   |                                               | 8              |

|               | 3.3   | The P   | CB artwork                                    | $\mathbf{S}^2$ |

|               |       | 3.3.1   |                                               | 34             |

|               |       | 3.3.2   | The LCD PCB                                   | 34             |

|               |       | 3.3.3   | The Latch and divider PCB                     | 6              |

|               |       | 3.3.4   | The GPIB PCB                                  | 87             |

|               |       | 3.3.5   |                                               | 9              |

|               |       | 3.3.6   |                                               | 0              |

|               | 3.4   | Assem   |                                               | 0              |

|               | 3.5   |         |                                               | 3              |

|          |                            | 3.5.1                           | The microcontroller and RAM module                                                       | 43                   |

|----------|----------------------------|---------------------------------|------------------------------------------------------------------------------------------|----------------------|

|          |                            | 3.5.2                           | The LCD module                                                                           | 44                   |

|          |                            | 3.5.3                           | The A/D and filter module $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ | 44                   |

|          |                            | 3.5.4                           | The GPIB module                                                                          | 47                   |

|          |                            | 3.5.5                           | The Latch and divider module                                                             | 49                   |

|          | 3.6                        | Proble                          | ems encountered with the hardware                                                        | 49                   |

| 4        | The                        | pulsa                           | r timer software                                                                         | 53                   |

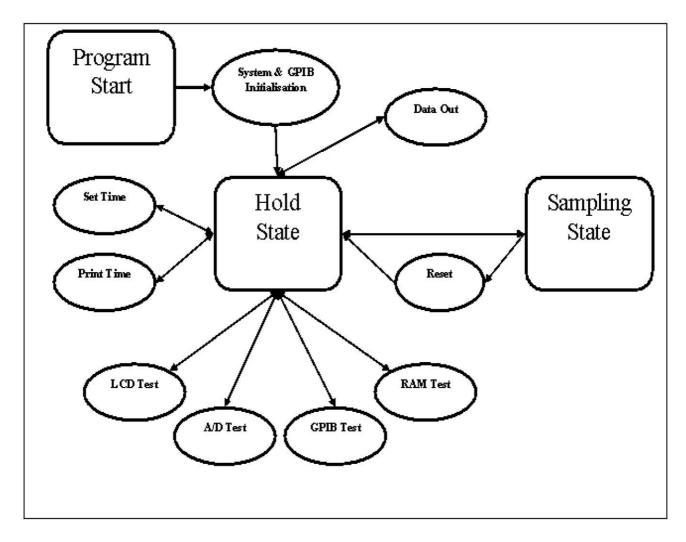

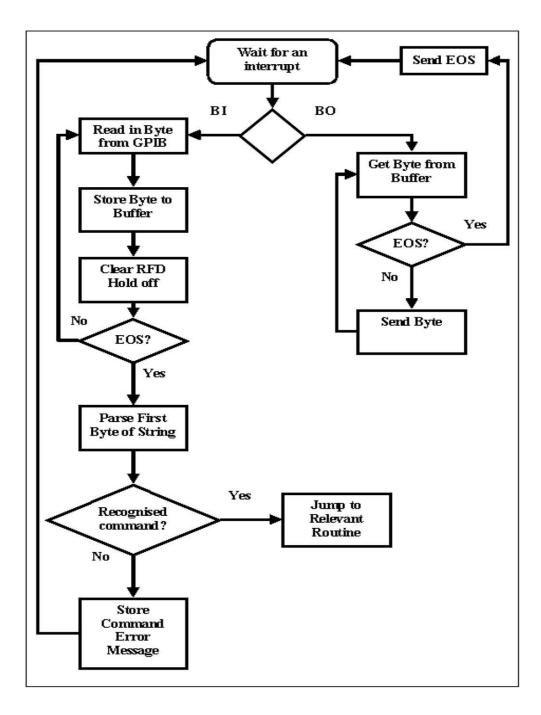

|          | 4.1                        | The G                           | PIB and system initialisation code units                                                 | 56                   |

|          |                            | 4.1.1                           | System initialisation                                                                    | 56                   |

|          |                            | 4.1.2                           | GPIB initialisation                                                                      | 56                   |

|          | 4.2                        | The h                           | old state code module                                                                    | 58                   |

|          | 4.3                        | The te                          | est and time control routines                                                            | 62                   |

|          |                            | 4.3.1                           | Test routines                                                                            | 62                   |

|          |                            | 4.3.2                           | Time management routines                                                                 | 64                   |

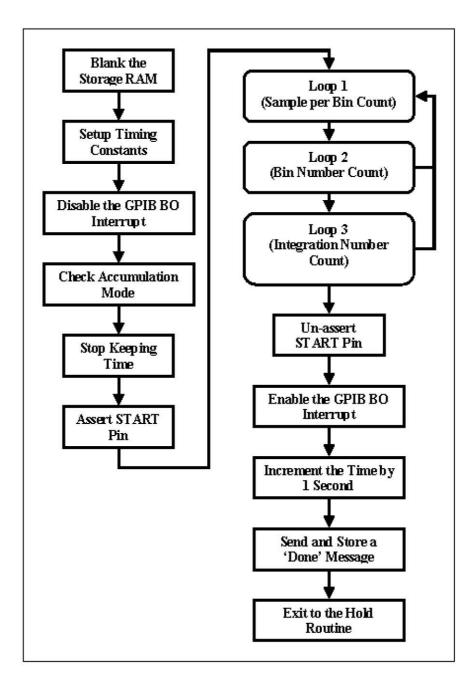

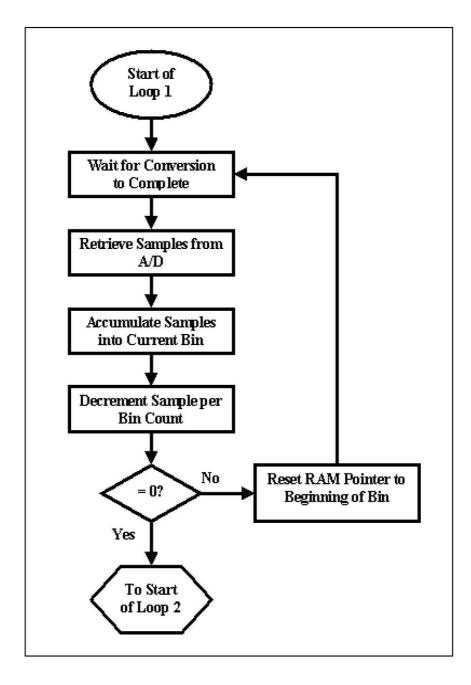

|          | 4.4                        | The sa                          | ampling state routine                                                                    | 65                   |

|          | 4.5                        | The da                          | ata output routine                                                                       | 71                   |

|          | 4.6                        | The L                           | CD software                                                                              | 73                   |

| <b>5</b> | Inst                       | allatio                         | on and testing of the new pulsar timer                                                   | <b>74</b>            |

|          | 5.1                        | Install                         | lation                                                                                   | 74                   |

|          | 5.2                        | Final s                         | system testing                                                                           | 78                   |

|          |                            | 5.2.1                           | Functionality testing                                                                    | 78                   |

|          |                            | 5.2.2                           | Radiometer equation compliance testing                                                   | 83                   |

|          |                            | 5.2.3                           | Timing accuracy testing                                                                  | 84                   |

|          |                            | 5.2.4                           | Performance comparison testing                                                           | 86                   |

| c        |                            |                                 |                                                                                          |                      |

| 6        | Opp                        | ortun                           | ities for future work                                                                    | 92                   |

| 6<br>7   |                            | oortun                          |                                                                                          | 92<br>93             |

| 7        | Con                        | clusio                          |                                                                                          | 93                   |

| 7        |                            | clusio                          |                                                                                          |                      |

| 7<br>Re  | Con<br>eferen<br>CD        | nclusion<br>nces<br>Appen       | n<br>ndix                                                                                | 93<br>94<br>96       |

| 7<br>Re  | Con<br>eferen<br>CD<br>A.1 | nces<br>nces<br>Appen<br>The co | n<br>ndix<br>ode folder                                                                  | 93<br>94<br>96<br>96 |

| 7<br>Re  | Con<br>eferen<br>CD        | nces<br>nces<br>Appen<br>The co | n<br>ndix                                                                                | 93<br>94<br>96       |

# List of Figures

| 2.1  | A synthetic period folding example.                                                                             | 8  |

|------|-----------------------------------------------------------------------------------------------------------------|----|

| 2.2  | Integrated profile for the synthetic period folding example                                                     | 8  |

| 2.3  | Flow diagram for calculating the timing constants                                                               | 10 |

| 2.4  | The integrating flow diagram.                                                                                   | 11 |

| 2.5  | Pulse profile showing a single pulse period                                                                     | 13 |

| 2.6  | Pulse profile showing multiple pulse periods.                                                                   | 13 |

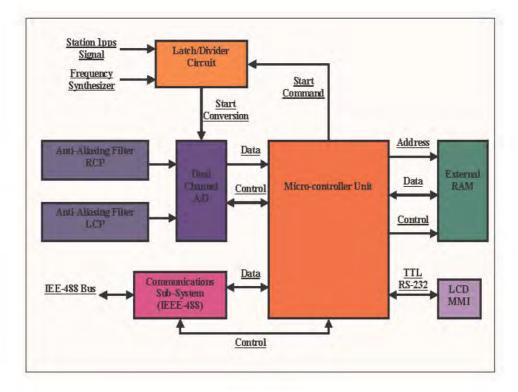

| 2.7  | Block diagram of the new pulsar timer                                                                           | 14 |

| 2.8  | Memory Map for the new pulsar timer RAM                                                                         | 16 |

| 3.1  | The hardware block diagram for the new device                                                                   | 20 |

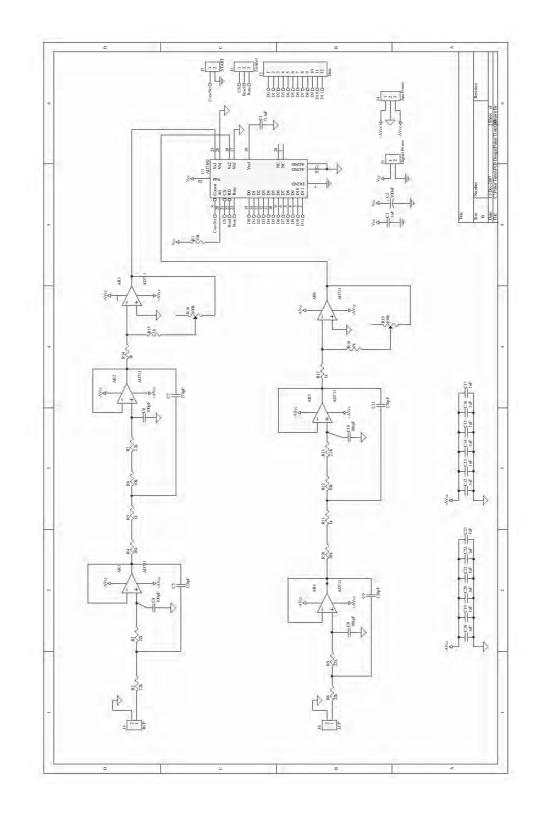

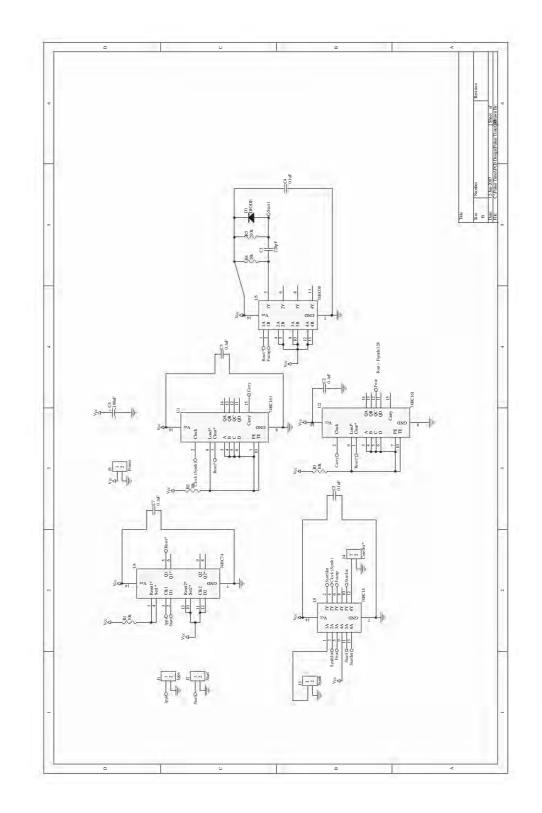

| 3.2  | A/D module schematic. $\ldots$ | 27 |

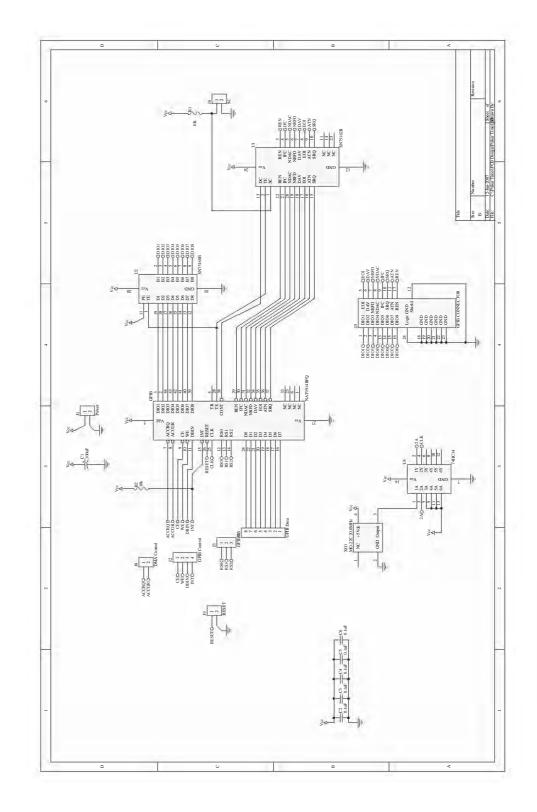

| 3.3  | GPIB module schematic.                                                                                          | 29 |

| 3.4  | LCD module schematic.                                                                                           | 30 |

| 3.5  | latch and divider module schematic.                                                                             | 31 |

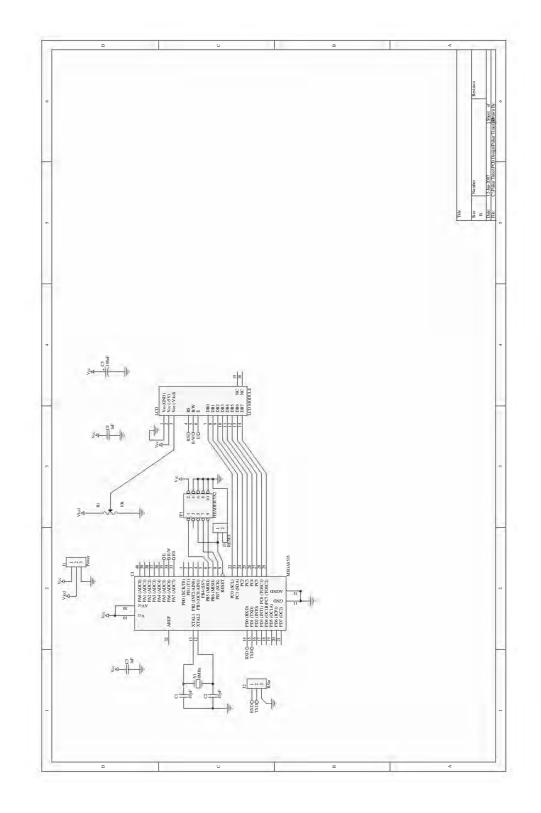

| 3.6  | Microcontroller module schematic                                                                                | 33 |

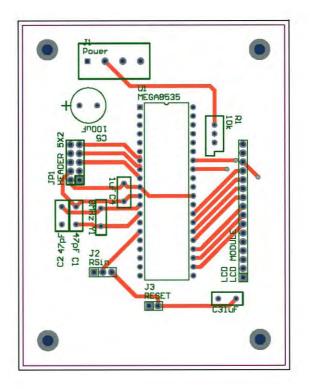

| 3.7  | Microcontroller board top layer artwork                                                                         | 34 |

| 3.8  | Microcontroller board bottom layer artwork                                                                      | 35 |

| 3.9  | LCD board top layer artwork                                                                                     | 36 |

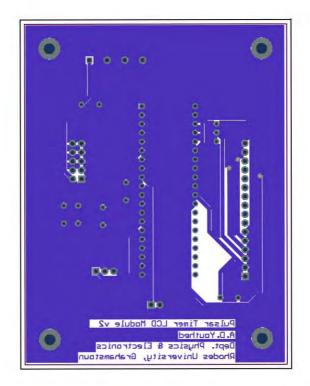

| 3.10 | LCD board bottom layer artwork                                                                                  | 37 |

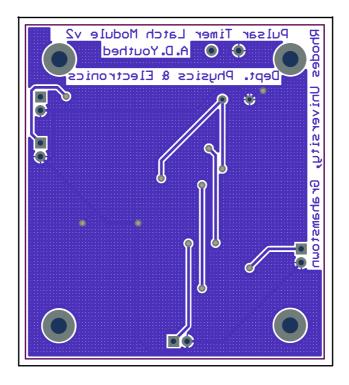

|      | latch and divider board top layer artwork.                                                                      | 38 |

|      | latch and divider board bottom layer artwork                                                                    | 38 |

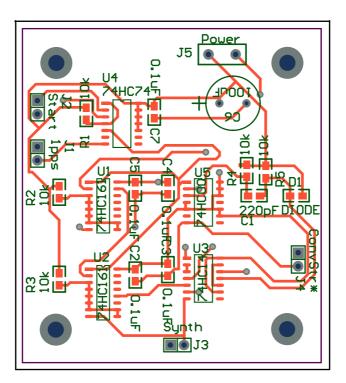

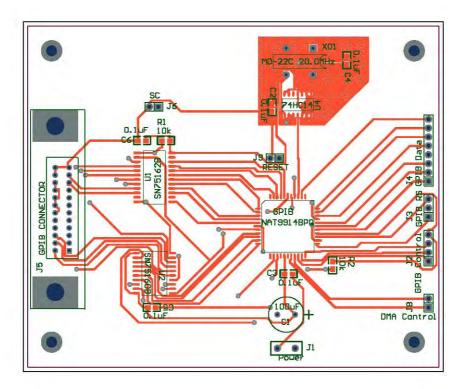

|      | GPIB board top layer artwork.                                                                                   | 39 |

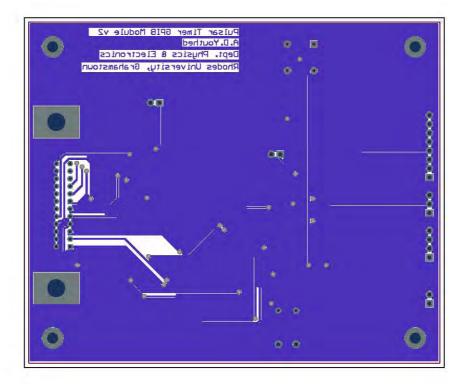

|      | GPIB board bottom layer artwork.                                                                                | 40 |

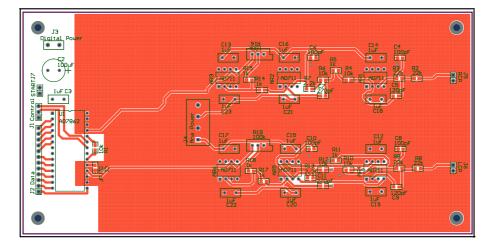

|      | A/D board top layer artwork                                                                                     | 41 |

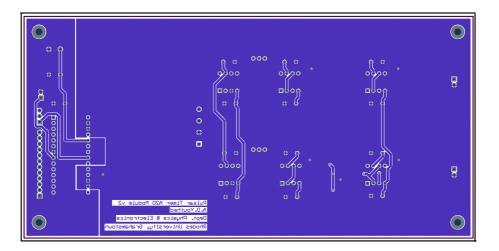

|      | A/D board bottom layer artwork                                                                                  | 41 |

|      | Anti-aliasing filter magnitude responses.                                                                       | 45 |

|      | 4-pole Bessel filter theoretical magnitude response                                                             | 46 |

|      | Anti-aliasing filter phase responses.                                                                           | 47 |

| 3.20 | 4-pole Bessel filter theoretical phase response                                                                 | 48 |

| 4.1  | Pulsar timer architecture diagram.                                                                              | 54 |

| 4.2  | Software state transition diagram                                                                               |    |

| 4.3  | The hold state flow diagram                                                                                     | 60 |

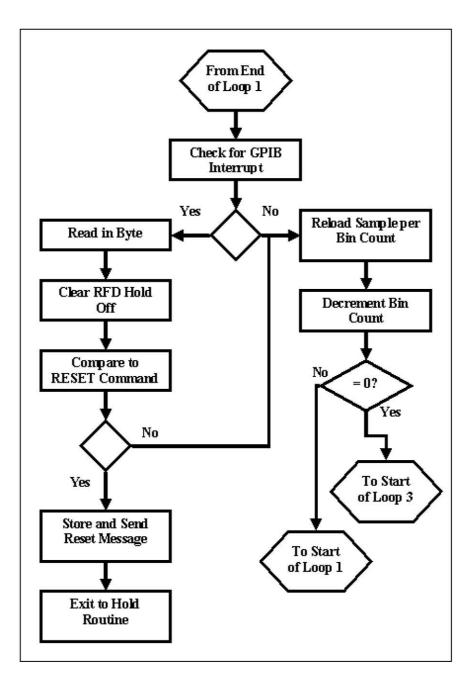

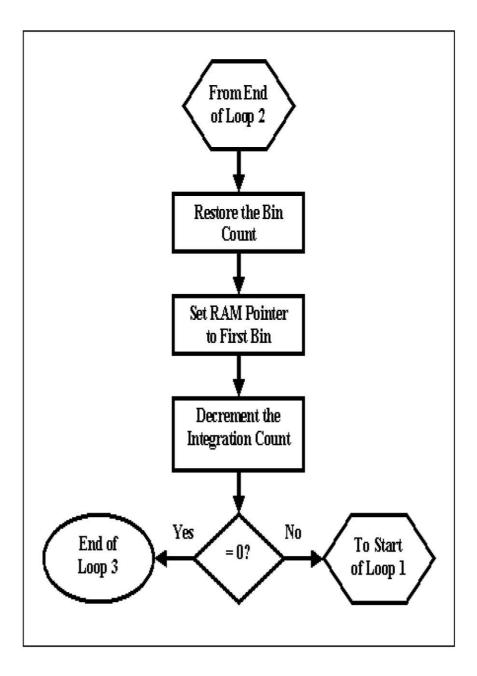

| 4.4  | The overall pulsar timer sampling routine                                                                       | 66 |

| 4.5  | The first loop of the sampling routine                                                                          | 67 |

| 4.6  | The second loop of the sampling routine                                                                         | 68 |

| 4.7  | The third loop of the sampling routine                                                                          | 69 |

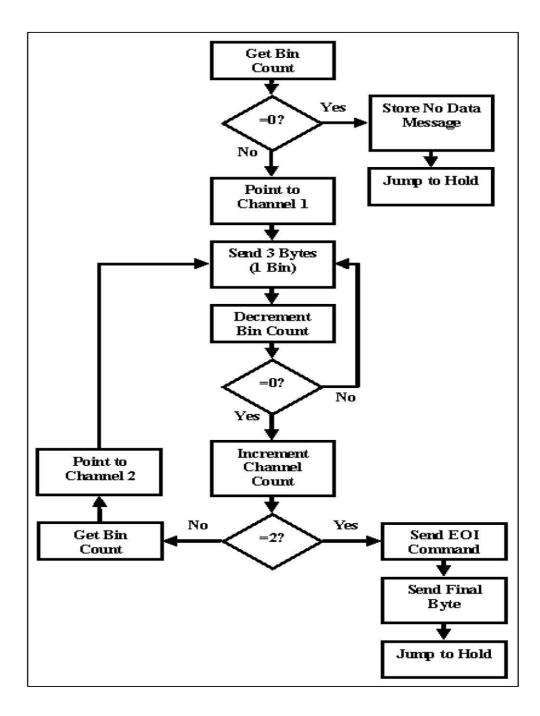

| 4.8  | The data output routine flow diagram.                                                                           | 72 |

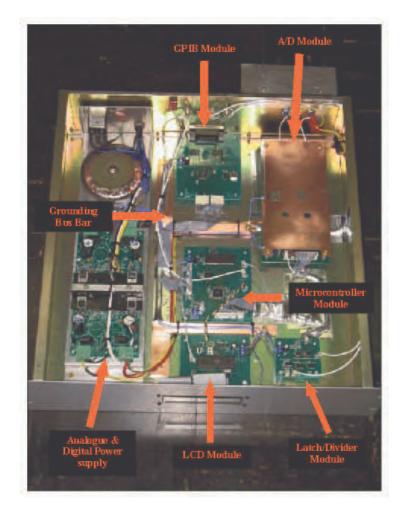

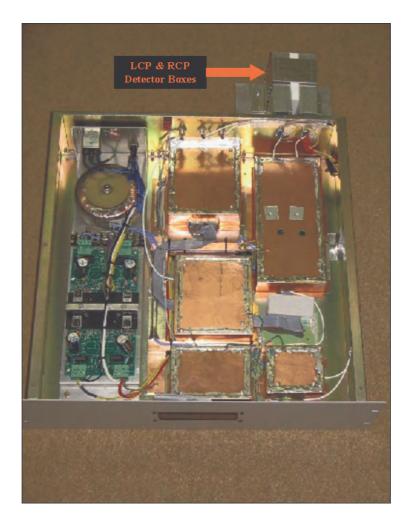

| 5.1  | New pulsar timer internals, before shielding                                                                    | 75 |

| 5.2  | The new pulsar timer internals, with shielding                                      | 76  |

|------|-------------------------------------------------------------------------------------|-----|

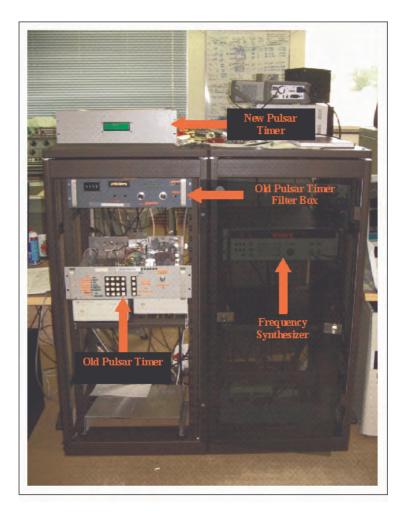

| 5.3  | Test setup of the new pulsar timer                                                  | 77  |

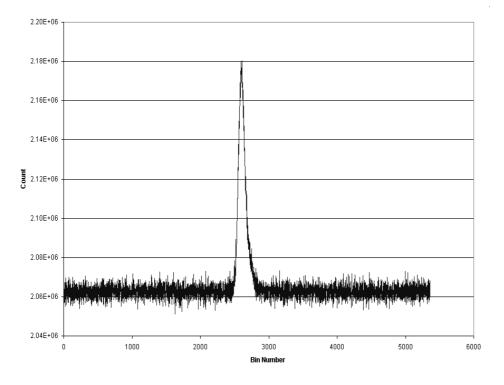

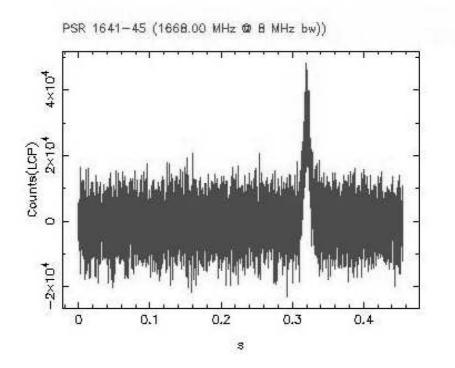

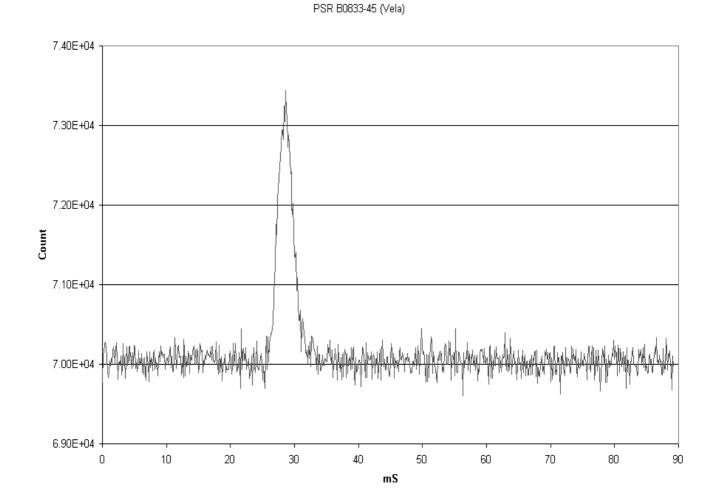

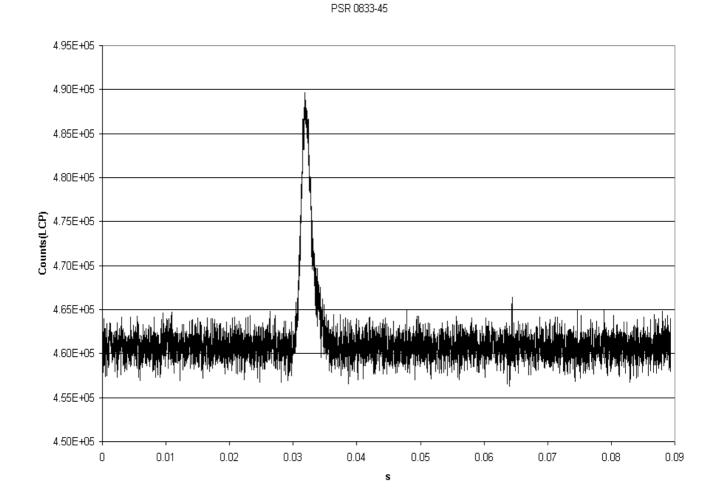

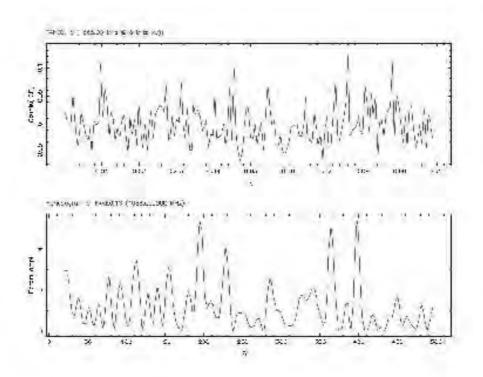

| 5.4  | The first integrated pulse profile obtained using the new pulsar timer              | 80  |

| 5.5  | Integrated pulse profile of PSR B0833-45 obtained using the old timer. $\therefore$ | 81  |

| 5.6  | Integrated pulse profile of PSR B0833-45 obtained using the new timer               | 82  |

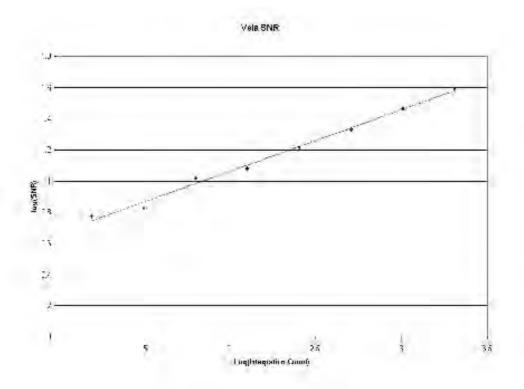

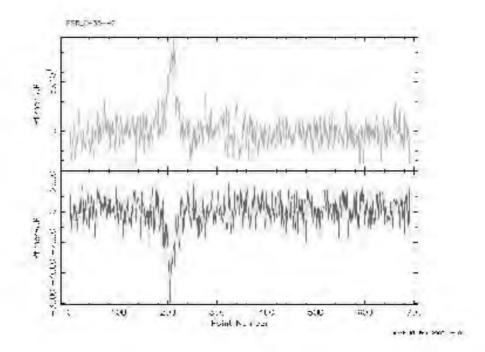

| 5.7  | The linear relationship between $\log(SNR)$ and $\log(BW \tau)$                     | 84  |

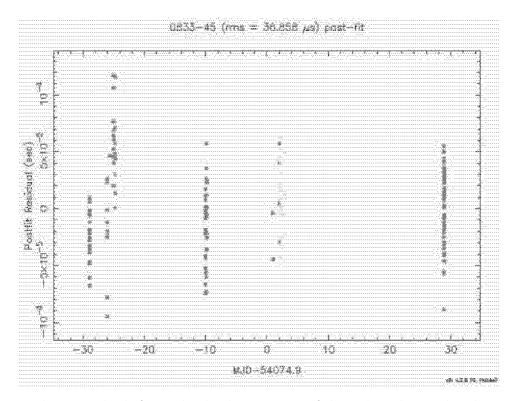

| 5.8  | A plot of phase residuals for PSR B0833-45.                                         | 85  |

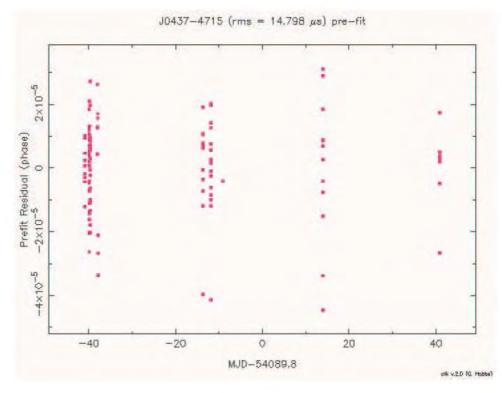

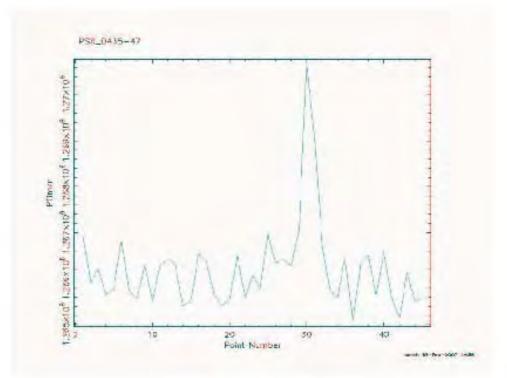

| 5.9  | A plot of phase residuals for PSR B0435-47                                          | 86  |

| 5.10 | Pulse profile of PSR B0435-47 produced using the old timer                          | 88  |

| 5.11 | Pulse profile of PSR B0435-47 obtained from the new timer                           | 89  |

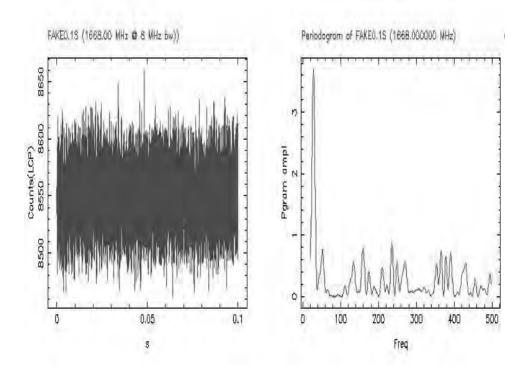

| 5.12 | The 60Hz integrated test profile and periodogram obtained from the old timer.       | 90  |

| 5.13 | The 60 Hz integrated test profile and periodogram obtained from the new             |     |

|      | timer                                                                               | 91  |

| B.1  | The A/D module printed circuit board                                                | 99  |

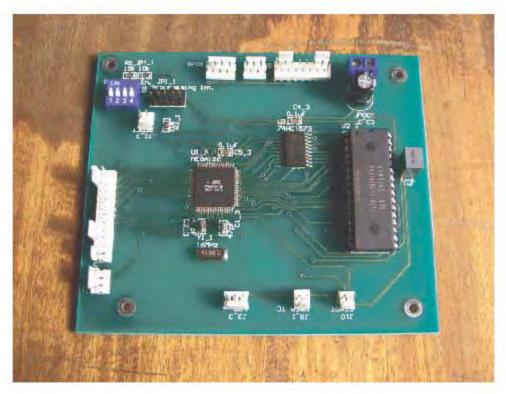

| B.2  | The Microcontroller module printed circuit board                                    | 99  |

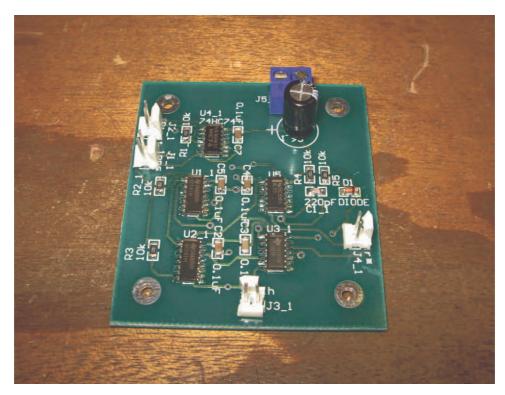

| B.3  | The GPIB module printed circuit board                                               | 100 |

| B.4  | The Latch and Divider module printed circuit board                                  | 100 |

| B.5  | The LCD module printed circuit board                                                | 101 |

# List of Tables

| 3.1 | I/O I | oin assignment | ts for the microcontrol | er | 24 |

|-----|-------|----------------|-------------------------|----|----|

|-----|-------|----------------|-------------------------|----|----|

# Chapter 1 Introduction

### 1.1 What are pulsars?

A pulsar, or neutron star, is the collapsed core of a star and is formed by the gravitational collapse of the core during a supernova. A pulsar's canonical mass is approximately 1.4 solar masses and their radii of the order of 20 km [1, pg 57-58]. From this one can deduce that pulsars are extremely dense objects. Using these canonical values, the density can be shown to be almost 3 times that of nuclear matter [1, pg 58-59]. It has been suggested that pulsars consist primarily of a neutron superfluid with a crystalline iron crust, hence the name neutron stars.

Due to the high densities and high rotation rates of these objects, the angular momentum is large. This leads to very stable rotational periods. The rotational period of pulsars vary from seconds to milliseconds, depending on the rotational energy and the age of the star. The period of most pulsars is determined by the initial rotational period and the spin down that occurs over time. 'Millisecond' pulsars normally form from binary star systems. The pulsar is spun up by mass transferal from its binary companion. The shortest period pulsar observed from HartRAO is PSR B0435-47 with a period of approximately 5.8 ms and the longest is PSR B2045-16 with a period of approximately 1.96 s.

It is commonly accepted that the radio beams emitted by pulsars emanate from heated particles trapped in the very intense magnetic fields at the pulsar's poles. If the pulsar spins about an axis that is not aligned with the magnetic axis, then the electromagnetic beams sweep a circular path over the surrounding space much like a lighthouse. If one resides within the beam path, then the electromagnetic radiation would appear as a burst of energy as the beam sweeps past. Given the large angular momentum of these stars, their spin periods are very stable. This means that the arrival time of the received pulses are predictable to great precision over time. Due to the large separations between us and these pulsars, as well as the attenuation and dispersive effects of the interstellar medium, these pulses can be very weak. To observe these pulsars and to gain spin period information from them, special techniques need to be employed to boost the Signal to Noise Ratio (SNR) of the pulses. These techniques are generally known as pulsar timing techniques and the spin period information is obtained by accurately measuring the arrival time of the pulses emitted by the pulsar.

# 1.2 Should a pulsar timer really be called a pulsar timer?

For a pulsar timer to be true to its name sake, it would have to provide the period of the pulsar under observation. This, in general, is not the case. Most pulsar timers produce a pulse profile of the pulsar being observed. The pulse profile is synchronised to an accurately known reference time. The pulse period is then obtained from the Time of Arrival (TOA) of the pulse in the pulse profile. More detail on finding the TOA for a pulse profile is given in Chapter 2.

The pulsar timer does not produce the period of the pulsar as a primary output. However, as pulsar timers are the equipment used to obtain pulsar periods, even indirectly, they are still known as pulsar timers.

Integration based pulsar timers, such as this one, seem to be counter intuitive. To obtain the required integration timing accuracy, the pulse period of the pulsar being observed needs to be known accurately. This means that the pulse period needs to be known in order to obtain the pulse period. At first glance this seems to be a catch-22 situation. Due to the precise timing predictability of pulsars, the pulse period can be determined very accurately over a long period of time with the aid of a good pulsar model. It is this predicted pulse period that is used to set up the integration time. This method of pulsar timing may seem a bit fragile, but a big advantage of this method is that spin irregularities, or glitches, can be rapidly detected by a shift in the TOA of the pulse.

### **1.3** Motivations for a new pulsar timer

Pulsar timing at HartRAO has been carried out primarily with a period folding pulsar timing device. This device was designed and implemented as part of a PhD project to study glitches in the Vela pulsar in the early 80 s [2]. This device has been running pulsar observations ever since. As a result the existing pulsar timer uses, by modern standards, outdated technology. This has proven to be a problem in terms of maintaining the device. In an attempt to keep the existing device running, extensive modifications have been made to it over the past 20 years. These modifications, although successful, have added to the reliability problems of the existing device.

A list of the problems suffered by the existing pulsar timer is shown bellow:

- The original pulsar timer at HartRAO was built to observe the Vela pulsar and is being utilised for general pulsar observations which is a task it was never designed for.

- The sampling frequency of the existing pulsar timer is to low for observing millisecond pulsars accurately.

- Due to the extensive modifications and additions to the timer to keep it running, the hardware has become unstable and requires constant attention.

- The existing pulsar timer contains obsolete components and is thus very difficult to maintain.

- There is only one set of the hardware, with no backup for redundancy.

- A copy of the firmware for the existing device is not available, which makes system modification impossible without re-writing the firmware.

- The existing timer suffers from some serious Electro-Magnetic Interference (EMI). A large portion of this EMI is leakage from the 110 V, 60 Hz supply used at the observatory and can causes problems for observations of weak pulsars at or near a harmonic of 60 Hz.

A digital de-dispersion pulsar timer was designed and built for HartRAO as part of a PhD project to study the torqued precession in radio pulsars [3]. This device was only ever implemented for testing and was never installed at the observatory, but a system based on the Berkeley IBOB platform is being investigated.

Due to the reliability issues of the existing pulsar timer and the absence of the dedispersion timer, a temporary replacement device was called for. This device is intended to solve as many problems with the existing device as possible, while providing time for the full implementation of the de-dispersion timer at HartRAO. The specifications for the new device were provided by the HartRAO staff and are listed below:

- The new device should operate in a similar way to the existing device and must be a direct drop in replacement for the existing device.

- The new device should utilise more modern components for easy maintenance.

- The new design should be modular for easy maintenance and repair.

- The new timer should utilise surface mount technology, where ever possible, to improve the noise immunity of the device.

- The new pulsar timer should run at a higher sampling frequency than the existing timer to allow timing of millisecond pulsars and provide better timing resolution for all pulsars. The sampling cycle time should be between 7  $\mu$ s and 10  $\mu$ s.

- The new device should utilise an Atmel ATmega128 AVR microcontroller and implement a General Purpose Instrumentation Bus (GPIB) communications system using a NAT9914 GPIB controller.

- The new pulsar timer should sample two channels simultaneously using an AD78662 12-bit Analogue to Digital converter (A/D). This will allow for dual polarisation or dual frequency pulsar observations.

It should be noted that this device is intended as a temporary replacement for the existing device until a de-dispersion device can be implemented at the observatory.

Implementing a device similar to the existing timer at HartRAO poses a significant problem in terms of available literature. De-dispersion devices are considered standard equipment for timing pulsars [19] & [20] and as a result there is almost no open literature that is pertinent to this project.

This project aims to develop a device that will provide:

- Improved robustness.

- Improved reliability.

- Improved accuracy while utilising the current observation system.

- Easier maintenance.

- Drop-in compatibility with the current observation system.

# Chapter 2

# Functionality and technologies used

The function of a pulsar timer is to take regular samples of a radio signal and produce an integrated profile of the signal. This is done by folding the time series using the nominal pulse period. The TOA for the pulse is found by fitting a pulse template to the integrated pulse profile and then measuring the time from the start of sampling to the pulse peak. The TOA is then used to determine the pulse period at the time of that observation. The error in the TOA depends on the intrinsic pulse width and SNR of the pulsar. This relationship is shown in equation 2.1 [1, pg 202].

$$\delta_{TOA} = \frac{\text{Pulse Width}}{\text{Signal to Noise Ratio}}$$

(2.1)

From this equation one can see that, with a fixed pulse width, the SNR of the pulse profile needs to be as high as possible for accurate TOA measurements. The pulse width of the received pulse is dependent on the dispersion measure for the pulsar. Dispersive effects of the interstellar medium result in a broadening and reduction in amplitude of the received pulse. This broadening produces an increased error in the TOA measurements. To reduce this effect a de-dispersion timer can be used. The new device, as with the existing device, does not perform de-dispersion and thus the primary concern is the SNR.

The signal to noise ratio is defined in equation 2.2 as the ratio of the signal power to the noise power [6, pg 434]. Due to the weak nature of most pulsar signals, multiple pulses are integrated together to form the final pulse profile with the required SNR.

$$SNR = \frac{Signal Power}{Noise Power}$$

(2.2)

From equations 2.1 and 2.2 one can see that, to reduce the error in the TOA measurements, one needs to have a large signal amplitude over the noise amplitude. To gain this

7

signal increase over the noise one needs to integrate many individual pulse profiles into a single profile. The shape of pulsar pulses are also stochastic which means that, to obtain a reliable pulse profile, the pulses need to be averaged.

## 2.1 The functionality of a period folding pulsar timer

All pulsar timers stack individual pulse profiles to increase the SNR to a sufficient level. Pulsar pulse profiles are stochastic. For this reason pulse folding averages out features in the individual pulses. The stochastic process is stationary so that the average pulse profile is constant over time, as long as enough integrations are done. This means that fine detail in the individual pulses are lost, but the pulse profile is not broadened. Both the existing and the new pulsar timers are period folding integration devices. An integrated pulse profile is sufficient for pulsar timing but not for observing finer pulse structure as explained above. These devices are also limited in their accuracy for pulsars with high dispersion measures. To allow the observatory to observe these pulsars, the de-dispersion device is needed.

A period folding integration timer samples the output from the radio receiver and stores the digital samples into an array of fixed length. If the array is sufficiently long, then the pulse peak will reside within the array. By choosing the length of the array carefully, one can ensure that the pulse peak occurs at the same position within the array each time new samples are accumulated into the array. This leads to the pulse value in the array growing at a higher rate than the noise. This integration process is repeated until the desired SNR is reached. The resulting array contains the integrated pulse profile of the pulsar.

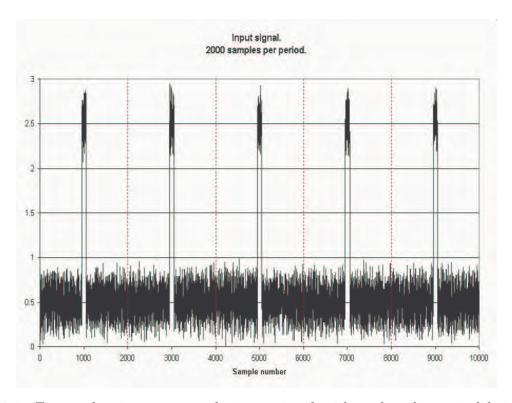

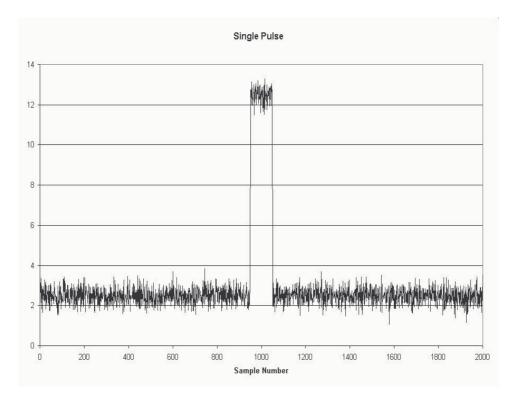

Figure 2.1 shows a synthetic example of an input signal before period folding is performed. From this figure one can see that each pulse period occupies a space of 2000 samples. This implies that each set of 2000 samples can be added to the following set to produce a single profile 2000 sample wide. This final profile is then the integrated profile for that pulsar signal. Figure 2.2 shows the integrated pulse profile for this synthetic example. The integration process is done a sample at a time in the pulsar timer. From this example one can see that the period folding technique increases the SNR of the pulse profile while maintaining the period of the pulsar signal.

Figure 2.1: Figure showing an example input signal with each pulse period being 2000 samples wide.

Figure 2.2: Figure showing the integrated profile of the example input signal.

The frequency at which the accumulation switches from the last element in the array to the first must then exactly match the pulsar frequency. If one knows the exact time at which the sampling started, then the arrival time of the integrated pulse, relative to this time, can be obtained. The arrival time of the pulse is used to determine the pulse period of the pulsar. Obtaining the arrival time and the period of the pulsar is normally done externally to the pulsar timer, through some post processing of the pulse profile.

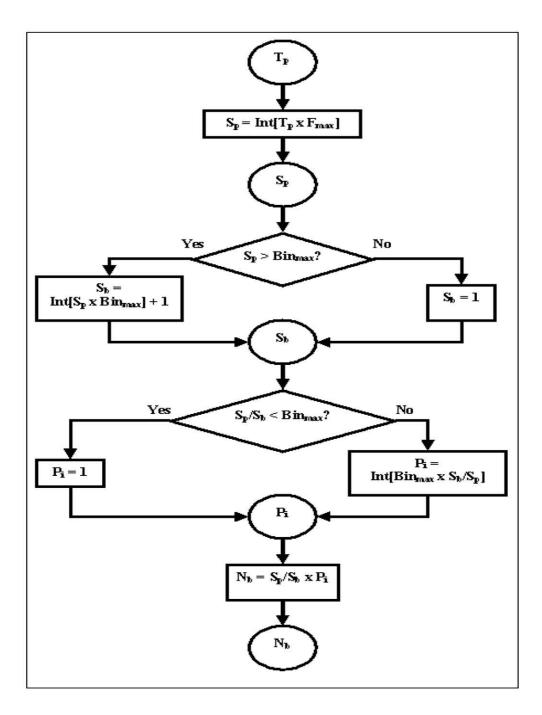

For a period folding pulsar timer, the array of binned profile samples is normally stored in RAM. A maximum limit is set to the number of bins within the memory as there can only be a fixed amount available to the system. The following list of variables are known as the timing constants for a pulsar observation:

- $S_p$  The total number of samples per pulse period.

- $S_b$  The number of samples to be stored in a bin per integration pass.

- $P_i$  The number of pulsar periods per integration.

- $N_b$  The number of bins used for the integration process.

- $N_I$  The number of integrations to perform.

These timing constants are calculated using the flow diagram shown in figure 2.3 as well as the pulsar period  $(T_p)$ , maximum sampling frequency  $(F_{max})$  and the maximum number of bins available  $(Bin_{max})$ .

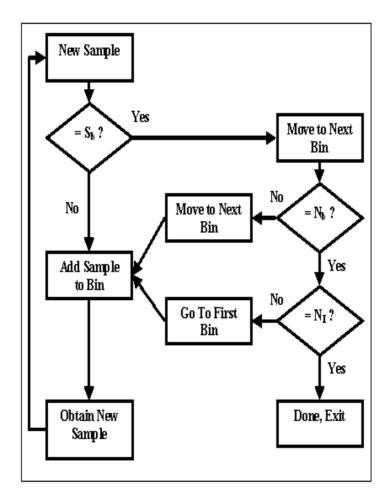

Figure 2.4 shows the overall integration process using the timing constants described above.

Due to the rounding errors introduced by taking the integer values for  $S_p$ ,  $S_b$  and  $P_i$ the sampling frequency must be modified to compensate. The actual sampling frequency,  $F_s$ , is found by equation 2.3 and will always be slightly lower than, but very close to, the maximum sampling frequency of the pulsar timer.

$$F_s = ((1/T_p) \times N_b \times S_b)/P_i \tag{2.3}$$

The number of integrations,  $N_I$ , to be taken is set by the astronomer to provide the required SNR and will vary depending on the relative strength of the pulsar being observed.

Figure 2.3: A flow diagram showing the process for calculating the timing constants required for timing a pulsar.

Figure 2.4: A flow diagram showing the integration process.  $S_b$  is the number of samples per bin,  $N_b$  is the number of bins and  $N_I$  is the number of integrations to perform.

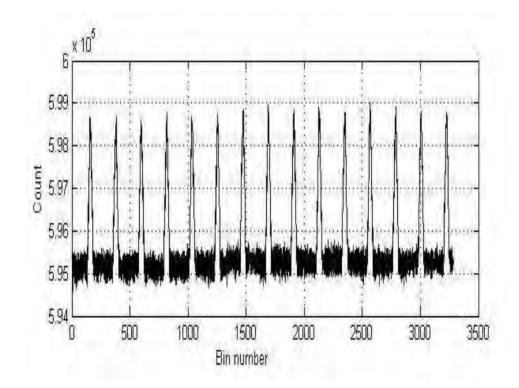

If the pulse period occupies significantly less than the maximum number of bins available, in other words if  $P_i > 1$ , then the integrated profile will contain  $P_i$  pulses. This is done in order to utilise the maximum amount of available storage memory at all times while maintaining a high sampling rate. This also allows for longer integrations before clipping occurs. The variation of  $P_i$  leads to two possible pulse profile configurations:

- A pulse profile containing a single pulse, as shown in figure 2.5.

- Or a profile containing multiple pulses.

Figure 2.6 shows a synthetic pulse profile that contains multiple pulses. One can see that each pulse resides in a fixed number of bins. There is always an integer number of pulses in a pulse profile, as set when calculating  $P_i$ . Knowing this one can calculate the number of bins each pulse occupies. Once this is known then the profile can be sectioned into individual pulses. These pulses can then be added together to form a single integrated pulse profile. This process is trivial to accomplish using the observation system. The single pulse profile is used to determine the arrival time of the pulse. The single pulse profile obtained by doing this also has a higher signal to noise ratio. The SNR is linked to the number of integrations used in compiling the single pulse profile. The integration count for single pulse profiles, obtained from multi-pulse profiles, is effectively the product  $P_i \times N_I$ .

The final integrated pulse profile can then be used to determine the TOA of the pulse and then the period of the pulsar. The pulsar period can then be used to study the pulsar's intrinsic spin behaviour o its astrometric parameters.

### 2.2 An operational outline of the new pulsar timer

This pulsar timer is required to be a direct drop in replacement for the old device and thus uses the same system interface This is done to eliminate the need for changes to the observation system, which the pulsar timer is connected to. The new pulsar timer is designed to take advantage of more modern components to provide the required speed, reliability and noise immunity improvements as highlighted in the specifications. Essentially this new device is an upgraded version of the existing device.

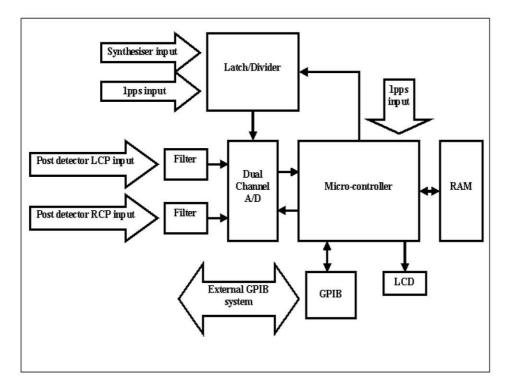

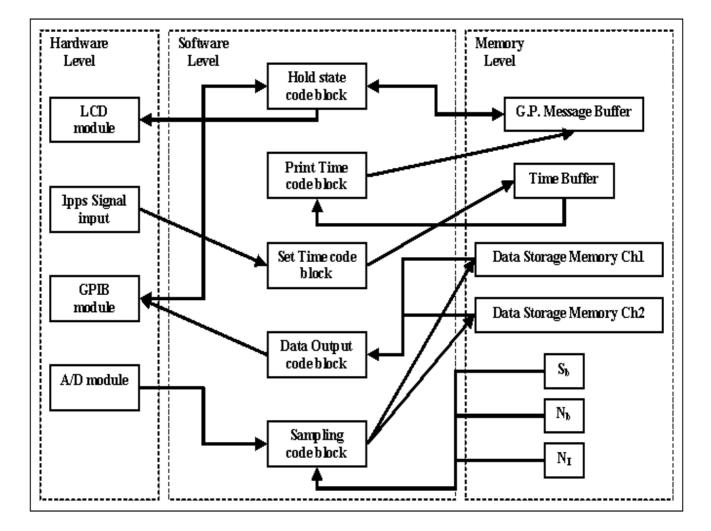

The general layout of the pulsar timer consists of seven distinct blocks. The basic block diagram for the new pulsar timer is shown in figure 2.7 and the functional blocks are highlighted below:

Figure 2.5: Pulse profile showing a single pulse period.

Figure 2.6: Pulse profile showing multiple pulse periods.

Figure 2.7: Block diagram of the new pulsar timer.

- A microcontroller to perform the accumulation of the samples and control all the other blocks.

- RAM to store the accumulated results.

- A communication unit to interface to the observation system. As required, an IEEE-488 instrumentation bus is used.

- A dual channel A/D to sample the analogue input signal.

- Two matching anti-aliasing filters to ensure that the Nyquist criterion is satisfied for the sampling system.

- A latch and divider circuit to decimate the synthesiser frequency and synchronise the A/D trigger pulse to the station 1pps signal.

- A Liquid Crystal Display (LCD) module to convey system messages and the device status to the user.

The microcontroller block serves as a control centre for all the other blocks of the pulsar timer. It retrieves samples from the A/D and accumulates the results, storing them to the RAM. It also controls the communications block that interfaces the pulsar timer to the observation system. The microcontroller block also sends text messages to the external LCD block. As the microcontroller block does the most work, it needs to be powerful enough to cope with all the tasks assigned to it.

The pulsar timer is designed to take samples of the analogue input signal and accumulate the samples into an array in RAM. The accumulation process calls for the microcontroller block to read the previous values from RAM, add the new samples and then store the new values back into the RAM. This involves a read and write cycle every time a new sample is taken. For this reason the RAM needs to be sufficiently fast. The microcontroller used in this project contains 4 kB of RAM, which is not large enough to store a sufficient number of samples. For this reason, external RAM is used. The microcontroller specified for this project supports up to a maximum of 60kB of RAM externally in combination with the 4kB internal RAM.

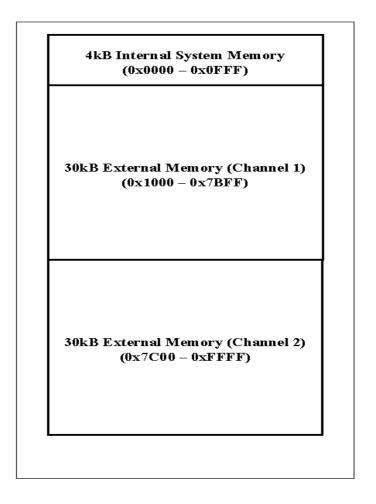

The RAM is divided into 3 separate sections. The memory internal to the microcontroller is used for system variables and message buffers. The remaining memory is used to store the integrated pulse profile.

The storage memory is divided into bins of fixed depth. The pulsar timer accumulates samples in two's complement signed binary format of 8 or 12-bits in length. The maximum number of samples that will be stored in each bin during the integration process is  $25 \times 10^4$  samples. Using the equation for random binary bit growth, equation 2.4, one can see that the minimum bin depth needs to be at least 20-bits.

$$2^{\text{(Sample bit count)}} \times \sqrt{\text{Sample Count}} = 2^{\text{(Bin bit depth)}}$$

(2.4)

To provide facility for longer integration times, a bin depth of 24-bits was chosen. With array lengths of 10000 bins per channel each channel will occupy 30 kB of memory space with both channels occupying 60 kB. The memory map for the RAM is shown in figure 2.8.

The GPIB block is the interface between the pulsar timer and the observation systems. Commands are received and data is sent via this interface. The communications scheme used is the IEEE-488 instrumentation bus, also known as Hewlett-Packard Instrumentation Bus (HPIB) or GPIB. This system allows the observation system to control the timer and other devices from the same bus and is the same communications scheme used in the

Figure 2.8: Memory Map for the new pulsar timer RAM.

existing pulsar timer.

The dual channel A/D block is responsible for taking the samples of the analogue inputs and passing the digital results to the microcontroller block. The A/D needs to be as fast as possible within the timing specifications of the pulsar timer. The faster the input signal can be sampled, the better the resolution for the final result. The specified A/D will provide sufficient sampling rate for the new device. The anti-aliasing filters are closely linked to the A/D block as these filters ensure that the incoming analogue signal bandwidth is in accordance with the Nyquist criterion. The Nyquist criterion ensures that the sampling frequency is high enough to prevent excessive aliasing of the analogue signal.

The sampling frequency for the pulsar timer needs to be very precise. This is to avoid smearing of the pulse profile as well as improve the accuracy of any measurements taken from the profile. The required accuracy is of the order of 10 significant figures. For this reason a frequency synthesiser is used to provide the sampling clock. To gain extra precision from the sampling clock, the synthesiser is run 128 times faster than required and the sampling clock is derived from the synthesiser frequency by dividing down. This is one of the primary functions of the latch and divider block. The latch and divider block also uses the 1pps signal, from the on site atomic clock, to synchronise the first A/D sample to an exact second. This ensures that the timing data can be accurately time stamped for later analysis and provides an accurate reference time for measuring the TOA for the pulse.

The LCD block is the Man Machine Interface (MMI) for the timer. It can be used to display system messages to the user and to inform the user as to which state the timer is in. As this block is not involved in the critical timing loop, there are no special requirements in terms of speed.

### 2.3 Technologies and features of the new pulsar timer

To obtain the greatest speed and flexibility from the new pulsar timer, full advantage is made of modern manufacturing technologies. These technologies allow for the implementation of a compact, reliable and noise resistant device. Some of the key technologies are highlighted below:

- Surface Mounted Devices (SMDs). These are electronic components that mount directly onto the surface of a printed circuit board without pins that protrude through the board. These devices are significantly smaller than their through hole counterparts and allow for components to be mounted on both board surfaces. These devices also boast better noise immunity than standard through hole devices.

- Dual Layer Printed Circuit Boards (PCBs) with through hole plating. Dual layer PCBs allow for the interconnecting tracks between components to be etched onto both sides of the PCB substrate. Dual layer PCBs simplify track routing and allow a designer to implement ground planes on the surfaces of the PCB. This improves overall noise immunity of the system, as well as reducing the noise radiated by the components on that board.

- Modern high speed microcontroller technology. The new pulsar timer makes use of a high speed Atmel RISC microcontroller. Most of the instructions need one clock cycle to complete which provides a very high clock cycle efficiency as well as very high data throughput capabilities.

The new pulsar timer makes use of a modular design philosophy. This allows for each separate functional block to be implemented as a separate module and greatly simplifies debugging and system maintenance. If the pulsar timer fails, the failure can be tracked quickly to a specific module. Once the faulty module is found, it can be replaced with a fully functional spare without disruption of the rest of the system. The faulty module can then be repaired with minimal down time to the system.

# Chapter 3

# The new pulsar timer hardware

In order to provide the required increase in resolution the pulsar timer has to collect, accumulate and store samples quickly. This sampling speed determines the specifications for the core sampling and accumulating components, namely the A/D, the microcontroller and the RAM. The microcontroller and A/D for this project have already been specified. This removes the need to select these components for the core sampling system on a performance basis. It is worth noting, however, that these components boast a much higher performance than the components in use in the existing device. The existing pulsar timer has a minimum sampling cycle time of 113  $\mu$ s. The target sampling cycle time for the new device is between 7  $\mu$ s and 10  $\mu$ s. Within one sampling cycle the device has to perform the following tasks:

- Sample the analogue input.

- Determine the correct location in memory to retrieve and store the accumulator value.

- Retrieve the accumulator value from the memory location.

- Add the new value to the accumulator value.

- Store the new accumulator value back to the memory location.

Figure 3.1 shows a block diagram of the device hardware and details the interconnections between each functional block. Components were selected according to the functional and interfacing requirements for each block.

Figure 3.1: This diagram highlights the main functional hardware blocks for the new pulsar timer as well as the interconnections between each block.

## 3.1 Component selection

### 3.1.1 A/D components

The specifications for the new pulsar timer called for a dual-channel A/D system as shown in figure 3.1. The component specified for this task is the AD7862 manufactured by Analog Devices. This device is capable of performing a maximum of  $250 \times 10^3$  conversions a second which is a conversion time of 4  $\mu$ s. This converter samples two separate inputs and performs the conversion on each simultaneously. It uses a successive approximation conversion scheme to provide a digital result with a resolution of 12-Bits. The digital output is provided on a 12-Bit wide parallel bus interface. The parallel interface can be seen as a disadvantage in most cases. However, in this case, a parallel interface provides for increased reading speeds from the A/D. As the microcontroller has to read the A/D within the timing cycle, the reading speed needs to be as fast as possible. A serial interface A/D would require too much time to transfer the digital value from the A/D to the microcontroller. Another solution would be to utilise an A/D on the microcontroller itself. This is not a viable option as the digital noise generated by the microcontroller core would induce to much noise into the analogue input. The AD7862 fulfills all the requirements for the A/D of this device.

### 3.1.2 Filters

The anti-aliasing filters are used to limit the signal bandwidth before the input of the A/D as shown in figure 3.1. This ensures that the sampling system obeys the Nyquist criterion. The Nyquist criterion states that the sampling frequency of the system must be at least double the highest frequency in the input signal to prevent excessive aliasing [6, page 775]. To prevent the anti-aliasing filter from broadening the pulse profile, a filter design with a non-dispersive linear phase response is needed. A linear phase response reverse Fourier transforms to a constant time delay for each frequency passing through the filter. This means that each frequency is delayed by the same amount and dispersion is kept to a minimum.

To achieve sufficient alias rejection, with a sampling frequency of 140 kHz, a cut-off frequency of 50 kHz was chosen for the anti-aliasing filters. This provides a maximum sampling cycle time of 10  $\mu$ s, which is within the sampling specifications of the new device. To provide sufficient band roll-off fourth order filters were chosen for the filter design. The filters were implemented using a standard Bessel active filter design [5] to provide the required linear phase response. To improve the noise immunity and signal integrity of the signal, high precision AD711 op-amps were chosen for use in the active filters design.

#### 3.1.3 Communications sub-system

This hardware block, shown in figure 3.1, forms the control link between the PC-based observation system and the pulsar timer. This hardware block is not part of the core sampling structure. Its performance is thus determined by the post-accumulation data transfer speed and not the real-time sampling speed. Standard IEEE-488 components provide ample data rates and are thus used in this design. The specified communications chip used is National Instruments NAT9914 GPIB controller. Standard transceivers are used to interface the controller chip to the external GPIB bus as called for in the GPIB controller data sheet [13]. This hardware block is practically identical to the module used in the existing device with the exception that the GPIB controller is a more modern version.

### **3.1.4** Man machine interface

The LCD block is part of the communications system and is not a speed critical module. A standard 2 line, 16 character display is used and this is interfaced to a dedicated microcontroller. The microcontroller functions as a media translator between logic level serial data and the LCD module. The microcontroller chosen for this application was the ATmega8535. Unfortunately, at the time that the pulsar timer was built, no ATmega8535s were available. As a result an AT90S8535 is used as a substitute. The ATmega8535 is the new drop in replacement for the AT90S8535 and as a result, minimal code changes were needed to downgrade to the older microcontroller.

As shown in figure 3.1, Transistor Transistor Logic (TTL) level RS-232 signals were used between the main microcontroller module and the 8535 microcontroller in the LCD module. This provides a simple but effective communications system for the MMI. This communications scheme also provides a convenient way to debug the internal workings of the pulsar timer without using the GPIB communications module. Serial transceivers are a standard feature on modern microcontrollers and are thus a logical communication scheme to use for internal communications within a device.

### 3.1.5 Latch and divider

The latch and divider block is the timing interface between the programmable synthesiser output and the A/D module as shown in figure 3.1. It has to divide down the synthesiser frequency to the required sampling frequency, as well as ensure that the first sampling pulse is synchronised to the 1pps signal.

The synthesiser is capable of producing a maximum clock frequency of 20MHz with a frequency resolution of 1mHz. This gives a precision of  $2 \times 10^{10}$ :1. To obtain a sampling clock with a precision of greater than  $1 \times 10^{10}$ :1, one needs a synthesiser frequency higher than 10 MHz. The nominal sampling frequency of the pulsar timer is 140 kHz. This means that, to gain enough precision, the latch and divider module requires a division factor of approximately 140. A division factor of 128 is easy to implement with a simple 7-bit binary counter and still ensures that the frequency synthesiser is operating above 10MHz.

The maximum frequency encountered by the latch and divider circuitry is between 10MHz and 20MHz. This requires that the logic Integrated Circuits (ICs) used have a sufficiently low propagation delay. For this reason high speed Complimentary Metal-Oxide-Silicon (CMOS) logic chips are used for the latch and divider module. To obtain the required division factor, two 4-bit synchronous, binary counter chips are used. When cascaded, these 4-bit counters form an 8-bit counter which provides a maximum division factor of 256 times. The sampling clock is synchronised to the station 1pps signal using a D-type latch and some simple logic. The logic used for the latching section is designed to ensure that the first sample is started exactly on the closest following 1pps edge after the latch module is enabled. This is to ensure that the sampling begins on a specific second for accurate time stamping of the accumulated data.

### 3.1.6 Microcontroller

The microcontroller for the system needs to handle all the processing requirements of the pulsar timer, as well as all the ancillary functions, such as communications. The microcontroller specified for use in this device is the Atmel ATmega128 microcontroller. This microcontroller operates at a maximum of 16MHz, has a transparent external RAM interface, two serial transceivers and a maximum of 53 usable Input/Output (I/O) pins with programable pull-ups. The external RAM interface can support a maximum of 64 kB external RAM, which is sufficient for the purposes of this project. This microcontroller is an 8-bit RISC controller, with most of the instructions taking only one clock cycle to execute. Using equation 3.1 one can see that between 112 and 160 instruction cycles are available during the specified sampling cycle time.

$$N_{\rm instructions} = T_{\rm sampling} \times F_{\rm microcontroller} \tag{3.1}$$

Table 3.1 shows a list of the I/O pins available on the microcontroller and their assignments. As one can see, this microcontroller fits the I/O specifications suitably for this application.

| Device          | Signal Name               | Number of I/O pins |

|-----------------|---------------------------|--------------------|

| External Memory | Address (low byte) + Data | 8                  |

|                 | Address (high byte)       | 8                  |

|                 | Address Latch Enable      | 1                  |

|                 | Read                      | 1                  |

|                 | Write                     | 1                  |

|                 |                           |                    |

| IEEE-488        | Data                      | 8                  |

|                 | Register Select           | 3                  |

|                 | Interrupt                 | 1                  |

|                 | Write Enable              | 1                  |

|                 | Chip Enable               | 1                  |

|                 | Read Enable               | 1                  |

| A/D Converter   | Data (high byte)          | 4                  |

|                 | Data (low byte)           | 8                  |

|                 | Chip Enable               | 1                  |

|                 | Read                      | 1                  |

|                 | Busy                      | 1                  |

| MMI             | Data RX                   | 1                  |

|                 | Data TX                   | 1                  |

| General I/O     | Start Command             | 1                  |

|                 | 1 Pulse per Second        | 1                  |

|                 | Total I/O pins required:  | 53                 |

Table 3.1: This table lists the I/O pin assignments for the microcontroller for interfacing to all the modules in the device.

#### 3.1.7 Memory

The ATmega128 uses a parallel interface for the external RAM. This is ideal for high speed, time critical applications such as this one. The microcontroller is capable of completing a read or write cycle to RAM in a minimum of 2 clock cycles [8] on a parallel interface. This means that the RAM should have a latency of less than 125 ns. The ATmega128 can support a maximum of 64 kB of external RAM. The Samsung 70 ns RAM module meets the speed requirements with performance to spare. Unfortunately, at the time of manufacture, no 64 kB RAM was available from Samsung. For this reason a 128 kB RAM chip is used as a substitute. This leaves half the available memory unused by the microcontroller and allows for a future upgrade without requiring major hardware changes.

The interface between the microcontroller and the external RAM requires an address/data latch. A 74HC573 manufactured by SGS-Thomson Microelectronics is used to fulfill this function. This is a standard octal latch with a propagation delay of 18 ns. As the RAM cycle time is 125 ns, this latch is more than fast enough for this application.

## 3.2 Detailed design and schematic diagrams

The new pulsar timer consists of five separate modules, namely:

- A/D module. This module contains the A/D as well as the anti-aliasing filters for each channel.

- latch and divider module. This module contains all the logic required to convert the synthesiser signal into the A/D sampling clock as well as synchronise the sampling clock to the 1pps signal.

- Microcontroller module. This module contains the main system microcontroller as well as its associated external RAM.

- IEEE-488 Communications module. This module contains the controller and logic used to implement the GPIB communications scheme.

- The LCD module. This module contains the dedicated LCD microcontroller which implements the MMI.

The schematic diagram for each module details the interconnections required to implement the functionality of the module, using the chosen components for that module. Passive components were added to the schematics to provide pull-up, decoupling and smoothing where required. For convenience, the data sheets for the components used are included on the attached compact disc. The included data sheet listing is shown in Appendix A.

### 3.2.1 A/D and filters

The anti-aliasing filters were laid out on the same board as the analogue to digital converter to allow all of the analogue components to be separated from the majority of the digital components. Doing this reduces the chance of inducing digital noise into the analogue subsystem. Designing the filters on the same board as the A/D also allows the filters to be placed as close to the A/D as possible. This reduces the chance of induced interference on the signal paths between the filters and the A/D. The anti-aliasing filters for the existing pulsar timer are housed in a separate enclosure away from the main timer box. This means that this new timer replaces the old filter box as well as the existing pulsar timer box.

An amplifier is added to each of the outputs of the Bessel filters to boost the post filtered analogue signal. The gain of this amplifier is adjustable, to suit the input specifications of the A/D. The filters are designed as two stage, 4-pole filters, using the Sallen & Key architecture [5, pg 16-14 to 16-16]. The pin connection specifications for the Op-amps were obtained from the Op-amp data sheet [16].

The A/D schematic layout follows the A/D data sheet recommendations [7]. The data outputs are connected to a 12-pin SIP connector and the control lines are connected to a separate 3-pin SIP connector. These connectors allow for connections to be made between the A/D module and the microcontroller module with ribbon cables. The schematic sheet for this module is shown in figure 3.2 and demonstrates the linear layout of this module.

### 3.2.2 GPIB module

The component connections for the GPIB communications module were obtained from the GPIB controller chip data sheet [13], GPIB device application note [12] and the GPIB transceiver data sheets [14] and [15]. To generate the clock signal for the GPIB controller, a standard 20 MHz CMOS oscillator was used.

The logic level data lines are connected to a 8-pin SIP connector. The register select lines are connected to a 3-pin SIP connector and the control lines are connected to a

Figure 3.2: The schematic sheet for the Analogue to Digital converter module.

separate 4-pin SIP connector. These are connected to the microcontroller module with ribbon cables. The schematic for the GPIB communications module is shown in figure 3.3.

### 3.2.3 LCD module

The interconnections for the LCD module where obtained from the liquid crystal display data sheet [18] as well as the AT90S8535 microcontroller data sheet [9]. A 3 pin schematic connector is included to provide for RS-232 communications with the main microcontroller module. The schematic sheet for this module is shown in figure 3.4.

#### **3.2.4** Latch and divider module

The latch and divider module was designed using the information provided by the respective IC data sheets. On studying the A/D data sheet, it was noted that the A/D enters a low power sleep state if the 'Conversion Start' pin is held active for more than 4  $\mu$ s. The wake time from this sleep mode is of the order of 5ms. This is unacceptable for this application as the sampling time for the entire system is designed to be around 7  $\mu$ s. The problem is solved by implementing a differentiator on the output of the latch and divider module. This takes the sampling clock from the latch and divider module and provides a narrow activation pulse width of approximately  $2\mu s$  to the A/D. The components for the analogue differentiator were added to the latch module schematics with the intention of building the differentiator on the latch module board. Although this modification introduces an analogue section into a digital circuit, it is the simplest method to narrow the activation pulse. Using an analogue differentiator also helps to keep the overall part count for this module down. A lower part count will also ease debugging of the completed module. 2-Pin SIP connectors are added for the synthesiser input, the 1pps input, the sampling clock output and the start command input. Figure 3.5 shows the schematic sheet for the latch and divider module.

### 3.2.5 Microcontroller module

The interconnections of the components for the main microcontroller module were determined by consulting the data sheet for the ATmega128 [8], the data sheet for the external memory [10] as well as the address latch data sheet [17]. Each I/O pin on the ATmega128 microcontroller is capable of being programmed for internal pull-up. This helps to reduce the part count of the system by making external pull-up resistors unnecessary on all but

Figure 3.3: The schematic sheet for the GPIB module.

Figure 3.4: The schematic sheet for the LCD module.

Figure 3.5: The schematic sheet for the Latch and divider module.

a few of the pins. The following connectors where added to the schematic to provide connectivity between the microcontroller module and the other modules in the device.

- 12-pin SIP connector for the A/D data.

- 3-pin SIP connector for the control lines of the A/D module.

- 8-pin SIP connector for the GPIB data bus.

- 3-pin SIP connector for the register select lines to the GPIB controller.

- 4-pin SIP connector for the control lines to the GPIB module.

- 3-pin SIP connector for connection to the MMI module.

- 2-pin SIP connector for the 'START' command line to the latch and divider module.

- 2-pin SIP connector for the 1pps signal input to the microcontroller module.

An In System Programming (ISP) port was also added to the ATmega128 circuit design. This allows the microcontroller to be programmed in place and the code to be updated without the need for dismantling the entire system. Figure 3.6 shows the schematic sheet for the microcontroller module.

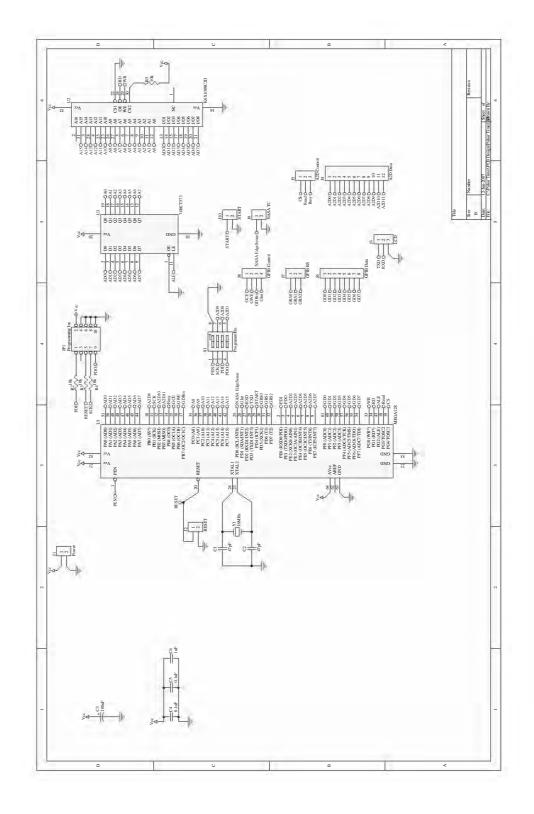

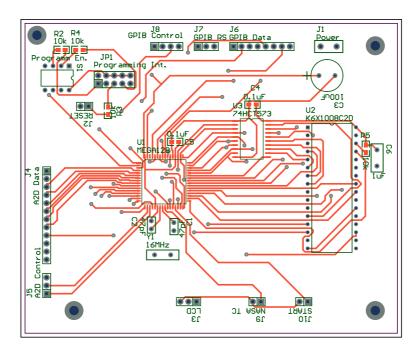

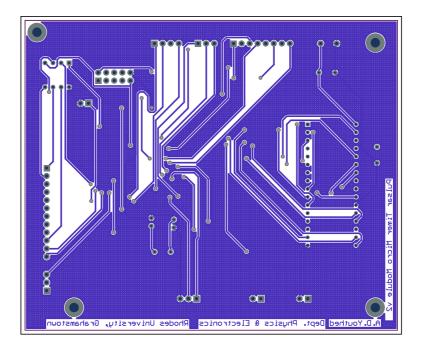

# 3.3 The PCB artwork

The PC board artworks were generated from the schematic sheets using the Protel Computer Aided Design (CAD) package. All the connections between the components are detailed in the schematic sheets. The components for each module are arranged to make the routing of the boards as simple as possible as well as reduce the possibility of induced noise between neighboring components. The power supply connections for each component were routed by hand to ensure direct low impedance current paths. The remaining connections were routed using the auto routing function in the CAD package. The auto routing system optimises the routing paths for the shortest possible distance between connections. For the first revision of the new pulsar timer boards, only the A/D board was designed with a ground plane. This was later changed and all the PCBs now contain at least one ground plane. The decoupling capacitors for each chip are placed as close to the chip as possible to trap supply rail transients.

Figure 3.6: The schematic sheet for the ATmega128 microcontroller module.

Figure 3.7: The top layer artwork for the ATmega128 microcontroller printed circuit board. Not to scale.

## 3.3.1 The Microcontroller PCB

The component arrangement for the microcontroller board is very simple because the component count is very low. The ATmega128 is placed near the centre of the board to ease routing to the connectors, which are placed at the edges of the board. The ISP port is placed toward one edge where it can be easily accessed to allow convenient reprogramming of the microcontroller unit. The microcontroller's crystal oscillator is positioned as close as possible to the controller in order to reduce EMI radiation from the microcontroller clock traces. The external RAM port on the microcontroller resides on one edge of the microcontroller chip, allowing the RAM to be positioned close to the microcontroller without causing routing complications. The address latch is placed between the RAM and the microcontroller. Figure 3.8 and figure 3.7 show the bottom and top layers of the final revision microcontroller module. Information on the modifications to the final revision boards can be seen in Section 3.3.6.

## 3.3.2 The LCD PCB

The LCD board is laid out with its microcontroller near the centre of the board. The connector for the LCD module is placed on a board edge to allow for easy connection using a ribbon cable. The serial transceiver connector is placed near the opposite edge. The ISP

Figure 3.8: The bottom layer artwork for the ATmega128 microcontroller printed circuit board. Not to scale.

port for this module is positioned for easy access. Figures 3.9 and 3.10 show the top and bottom layers of the final revision LCD board.

Figure 3.9: The top layer artwork for the Liquid Crystal Display printed circuit board. Not to scale.

## 3.3.3 The Latch and divider PCB

The components for the latch module are grouped to provide a logical layout. The counters are grouped together near the centre of the board, the latch near the top and the differentiator near one edge. The connector for the synthesiser input is placed so that the synthesiser signal path length on the board is as short as possible, to try and reduce radiation of the unbalanced and unshielded synthesiser signal once it reaches the board. All the remaining connectors are placed near the board edges to provide easy access for connection. Figures 3.11 and 3.12 show the top and bottom layers of the final revision latch and divider board.

Figure 3.10: The bottom layer artwork for the Liquid Crystal Display printed circuit board. Not to scale.

## 3.3.4 The GPIB PCB

The GPIB board is laid out in a linear format. The GPIB connector is placed on one edge of the board so that it can be mounted on the backplane of the chassis. The logic level data and control lines are placed on the opposite side to facilitate cable connection to the microcontroller board. This leads to a simple layout with the GPIB controller chip in the centre of the board and the transceiver chips placed between the GPIB connector and the GPIB controller. The controller's oscillator is placed off to one side, away from the data lines. Figure 3.13 shows the top layer of the final revision GPIB board and figure 3.14 shows the bottom layer of this board.

Figure 3.11: The top layer artwork for the Latch and Divider printed circuit board. Not to scale.

Figure 3.12: The bottom layer artwork for the Latch and Divider printed circuit board. Not to scale.

Figure 3.13: The top layer artwork for the General Purpose Interfacing Bus printed circuit board. Not to scale.

## 3.3.5 The A/D and filter PCB

The analogue to digital converter board is laid out in a linear format with the anti-aliasing filters on the left of the board and the A/D on the right. The input connectors are placed as close to the filter inputs as possible to try and reduce noise being induced into the input signal traces prior to the filter inputs. The filters and trimming amplifiers are laid out in a linear fashion toward the opposite edge of the board. The A/D chip is placed near the edge of the board with its data and control connectors placed at that edge to facilitate connection to the microcontroller board. This layout produces a convenient separation between the analogue and digital signal traces. The interface between the digital and analogue sides lies directly beneath the A/D chip. A split ground plane is implemented to isolate the analogue circuitry from the digital switching noise. The analogue power input and the analogue half of the A/D chip. The digital ground plane on the bottom layer of the board under the filters, amplifiers, analogue power input and the analogue half of the A/D chip. The digital supply and the digital half of the A/D chip. Figure 3.15 shows the top layer of the final revision A/D circuit board, figure 3.16 shows the bottom layer of this board.

Figure 3.14: The bottom layer artwork for the General Purpose Interfacing Bus printed circuit board. Not to scale.

## **3.3.6** The final revision artworks

During the installation and testing of the prototype some serious noise issues became apparent. As a result, for the final revision PC boards, extra ground planes were added to most of the boards. The GPIB, microcontroller, LCD and latch and divider modules all had ground planes added to the bottom layer of their PC boards. A small ground plane around the GPIB clock source was implemented on the upper layer of the GPIB module.

A mirror image of the analogue ground plane on the A/D module was placed on the upper surface of the A/D board. This was done to improve the EMI shielding of the analogue section of this board.

# 3.4 Assembly

Population of the PC boards was done one module at a time. It took approximately a week to completely populate all of the boards. Most of the boards use SMDs of some form. These were soldered into place using a surface mount soldering station and surface mount soldering paste. All the through-hole components where soldered into place using a standard soldering iron and standard flux core solder. When attempting to mount the

Figure 3.15: The top layer artwork for the Analogue to Digital converter printed circuit board. Not to scale.

Figure 3.16: The bottom layer artwork for the Analogue to Digital converter printed circuit board. Not to scale.

connectors and power supply binding posts to the circuit boards, it was noticed that the holes on the circuit boards were too small. This was caused by these components having square pin legs. On investigation it was found that the pin size for square leg components is quoted as a face to face measurement of the pin. The corner to corner measurement of the pin is then larger than the quoted size. The holes for these components could not be enlarged as the circuit boards use through-hole plating. Drilling out the holes to a larger diameter would remove any connection between the top and bottom copper layers. A temporary solution to this problem was to file down the corners of all the square pinned components! The holes for these components are then enlarged in the final revision of the PC boards. Pictures of the populated prototype boards are shown in Appendix B. Once the PC boards had been populated they were tested for functionality.

# 3.5 Testing the individual hardware modules

This section deals with the testing of each individual module for correct functionality. Where needed, small sections of code were written to allow the module to be tested in conjunction with the microcontroller module. This code was then later modified and used in the main system code. Chapter 4 shows details of the software design and the code segments used. Problems encountered in the design and testing procedures are highlighted in Section 3.6.

## 3.5.1 The microcontroller and RAM module

The microcontroller module contains two functional blocks, the microcontroller and the RAM. The microcontroller was tested for functionality first. This involved writing a small code block to test the pins of the microcontroller as well as the functionality of the onboard UART port. There after the RAM interface and RAM functionality was tested.

### Testing the microcontroller

Testing the microcontroller module required writing test software and programming the microcontroller. Some problems were encountered in programming the microcontroller and are highlighted in Section 3.6. The software for testing the pin functionality of the microcontroller simply involved toggling all the pins on the microcontroller at a fixed rate and with a known pattern. To test the serial transceiver port, a small program was written to echo any message sent by a computer terminal to the microcontroller, thus simultaneously testing both the transmit and receive capabilities of the serial transceiver.

#### Testing the RAM

Testing the RAM interface and functionality required the development of a RAM testing routine. To test the RAM, known ASCII characters were written to the RAM in an ordered fashion. The characters were written in blocks and sectors, a block being a fixed number of known characters and a sector being a fixed number of these blocks. The characters were then read from the RAM and checked against the original values written to the RAM. To simplify the test routine, sequential ASCII characters were chosen to be written to the RAM. These characters are 'A' through 'Z' followed by '[' as a control character.

Using a block per sector count of 223 and a sector count of 10, the final amount of RAM tested was 60210 bytes. This is slightly more than required but will cover the entire section

required for the data storage and accumulation. This test routine was later modified and used as the RAM test routine for the final pulsar timer code.

## 3.5.2 The LCD module

As with the ATmega128 testing, the first test for the LCD microcontroller was an I/O pin test. This was done in much the same way as for the main microcontroller module. A small program was written to toggle all the I/O pins on the LCD microcontroller with a fixed pattern. The LCD module has an onboard display driver that displays the required character for a specific byte code stored in its onboard RAM. The LCD microcontroller uploads the value for the character into the LCD RAM using an 8-bit wide parallel interface. The specifications for this interface are given in the LCD data sheet [18]. A short program was written to test the display and interface using a set of known characters. Once the interface had been tested and was working correctly the program was modified to take in characters, sent to the LCD microcontroller, via the serial transceiver. After sufficient testing, this program was then implemented in the final pulsar timer system. More information on the LCD code can be seen in Section 4.6.

## 3.5.3 The A/D and filter module

As the A/D module contains the filters as well as the A/D chip, the testing was done in two stages. The filters were tested first to ensure that they performed to specification. The A/D chip was then connected to the microcontroller module and tested to ensure that values could be correctly obtained from the A/D.

#### Testing the anti-aliasing filters

To test the filters the A/D chip was unplugged from the board and oscilloscope leads were attached to the input pins of the A/D socket to access the filter outputs. A variable frequency sinusoidal signal was provided by a programmable function generator simultaneously connected to the two filter inputs. The gain of the amplifiers between the filters and the A/D inputs were adjusted for this testing procedure. As these amplifiers provide a constant gain, the only noticeable effect would be a gain offset in the gain versus frequency plots. By comparing the input and output signals from each filter, gain and phase Bode plots were obtained.

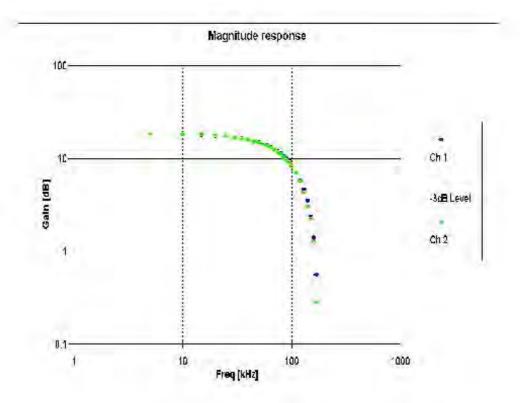

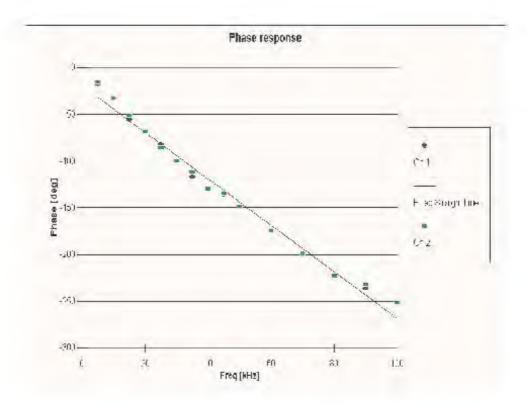

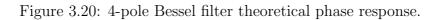

Figure 3.17: Anti-aliasing filter magnitude responses.

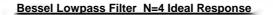

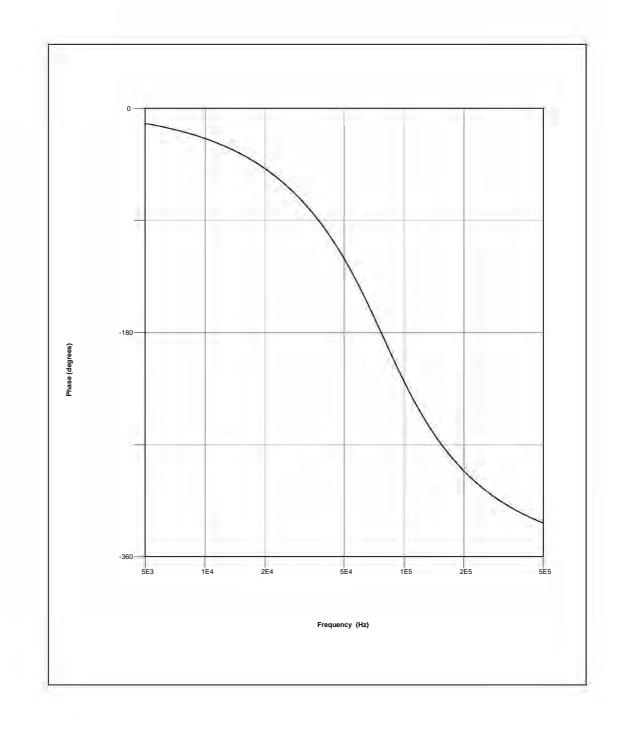

Figure 3.17 shows the gain plots for filter channels 1 and 2. Figure 3.18 shows the ideal filter gain response for these filters.

Figure 3.19 shows the phase response plots for filter channels 1 and 2. Figure 3.20 shows the ideal phase response for these filters.

The relatively slow roll-off of the filters is apparent from inspection of the magnitude response plots. The -3 dB point for each channel occurs at the specified frequency of 50 kHz for both filters. The phase response plots for each filter show the linear phase response which is typical of a Bessel filter.

#### Testing the A/D converter